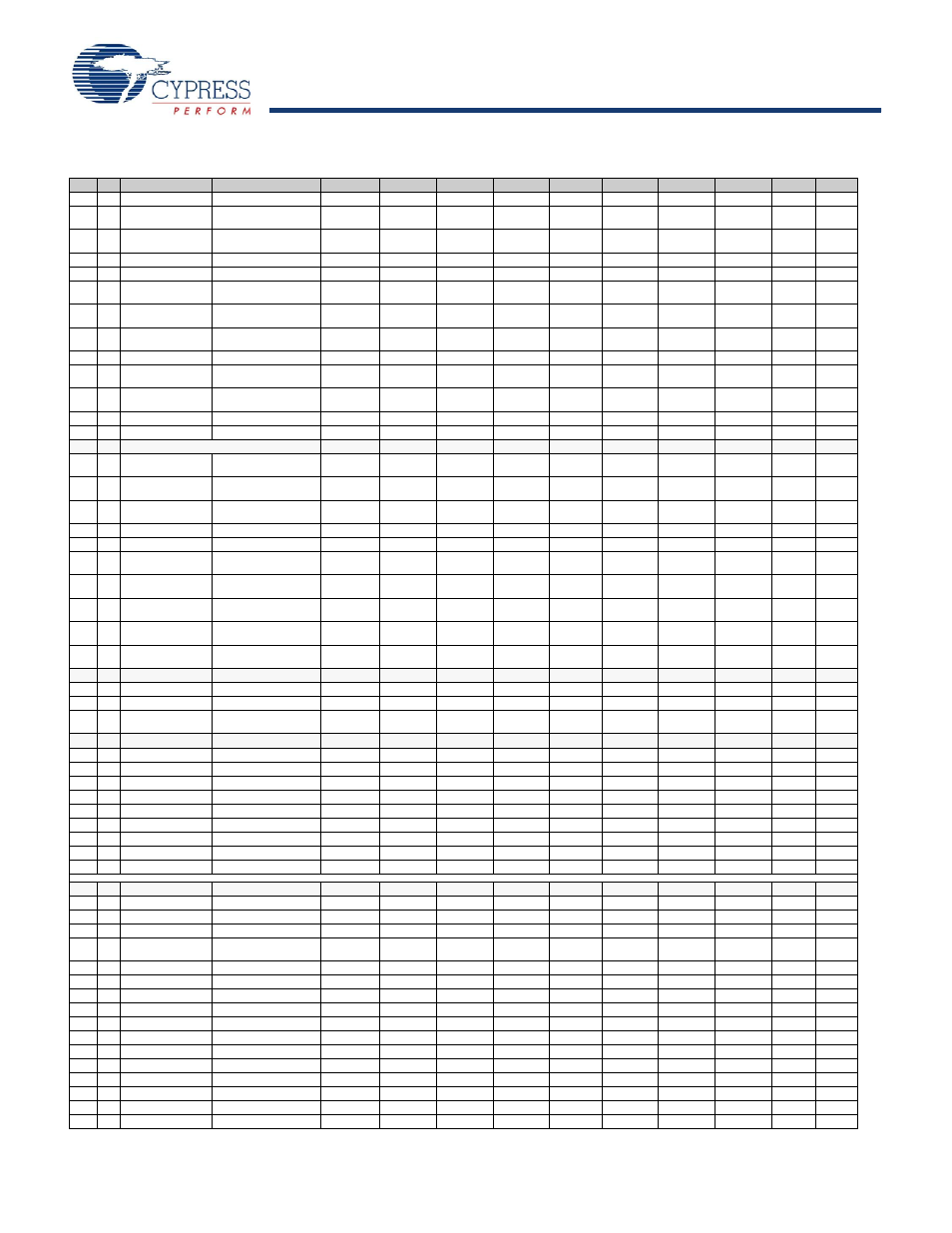

Table 12. fx2lp register summary (continued) – Cypress Perform CY7C68013 User Manual

Page 31

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

Document #: 38-08032 Rev. *L

Page 31 of 62

E65D 1

USBIRQ

USB Interrupt Requests

0

EP0ACK

HSGRANT

URES

SUSP

SUTOK

SOF

SUDAV

0xxxxxxx rbbbbbbb

E65E 1

EPIE

Endpoint Interrupt

Enables

EP8

EP6

EP4

EP2

EP1OUT

EP1IN

EP0OUT

EP0IN

00000000 RW

E65F 1

EPIRQ

Endpoint Interrupt

Requests

EP8

EP6

EP4

EP2

EP1OUT

EP1IN

EP0OUT

EP0IN

0

RW

E660 1

GPIFIE

GPIF Interrupt Enable

0

0

0

0

0

0

GPIFWF

GPIFDONE

00000000 RW

E661 1

GPIFIRQ

GPIF Interrupt Request

0

0

0

0

0

0

GPIFWF

GPIFDONE

000000xx RW

E662 1

USBERRIE

USB Error Interrupt

Enables

ISOEP8

ISOEP6

ISOEP4

ISOEP2

0

0

0

ERRLIMIT

00000000 RW

E663 1

USBERRIRQ

[12]

USB Error Interrupt

Requests

ISOEP8

ISOEP6

ISOEP4

ISOEP2

0

0

0

ERRLIMIT

0000000x bbbbrrrb

E664 1

ERRCNTLIM

USB Error counter and

limit

EC3

EC2

EC1

EC0

LIMIT3

LIMIT2

LIMIT1

LIMIT0

xxxx0100 rrrrbbbb

E665 1

CLRERRCNT

Clear Error Counter EC3:0 x

x

x

x

x

x

x

x

xxxxxxxx W

E666 1

INT2IVEC

Interrupt 2 (USB)

Autovector

0

I2V4

I2V3

I2V2

I2V1

I2V0

0

0

00000000 R

E667 1

INT4IVEC

Interrupt 4 (slave FIFO &

GPIF) Autovector

1

0

I4V3

I4V2

I4V1

I4V0

0

0

10000000 R

E668 1

INTSET-UP

Interrupt 2&4 setup

0

0

0

0

AV2EN

0

INT4SRC

AV4EN

00000000 RW

E669 7

reserved

INPUT / OUTPUT

E670 1

PORTACFG

IO PORTA Alternate

Configuration

FLAGD

SLCS

0

0

0

0

INT1

INT0

00000000 RW

E671 1

PORTCCFG

IO PORTC Alternate

Configuration

GPIFA7

GPIFA6

GPIFA5

GPIFA4

GPIFA3

GPIFA2

GPIFA1

GPIFA0

00000000 RW

E672 1

PORTECFG

IO PORTE Alternate

Configuration

GPIFA8

T2EX

INT6

RXD1OUT

RXD0OUT T2OUT

T1OUT

T0OUT

00000000 RW

E673 4

reserved

E677 1

reserved

E678 1

I

2

CS

I²C Bus

Control & Status

START

STOP

LASTRD

ID1

ID0

BERR

ACK

DONE

000xx000 bbbrrrrr

E679 1

I2DAT

I²C Bus

Data

d7

d6

d5

d4

d3

d2

d1

d0

xxxxxxxx RW

E67A 1

I

2

CTL

I²C Bus

Control

0

0

0

0

0

0

STOPIE

400KHZ

00000000 RW

E67B 1

XAUTODAT1

Autoptr1 MOVX access,

when APTREN=1

D7

D6

D5

D4

D3

D2

D1

D0

xxxxxxxx RW

E67C 1

XAUTODAT2

Autoptr2 MOVX access,

when APTREN=1

D7

D6

D5

D4

D3

D2

D1

D0

xxxxxxxx RW

UDMA CRC

E67D 1

UDMACRCH

UDMA CRC MSB

CRC15

CRC14

CRC13

CRC12

CRC11

CRC10

CRC9

CRC8

01001010 RW

E67E 1

UDMACRCL

UDMA CRC LSB

CRC7

CRC6

CRC5

CRC4

CRC3

CRC2

CRC1

CRC0

10111010 RW

E67F 1

UDMACRC-

QUALIFIER

UDMA CRC Qualifier

QENABLE

0

0

0

QSTATE

QSIGNAL2

QSIGNAL1

QSIGNAL0

00000000 brrrbbbb

USB CONTROL

E680 1

USBCS

USB Control & Status

HSM

0

0

0

DISCON

NOSYNSOF RENUM

SIGRSUME x0000000 rrrrbbbb

E681 1

SUSPEND

Put chip into suspend

x

x

x

x

x

x

x

x

xxxxxxxx W

E682 1

WAKEUPCS

Wakeup Control & Status WU2

WU

WU2POL

WUPOL

0

DPEN

WU2EN

WUEN

xx000101 bbbbrbbb

E683 1

TOGCTL

Toggle Control

Q

S

R

IO

EP3

EP2

EP1

EP0

x0000000 rrrbbbbb

E684 1

USBFRAMEH

USB Frame count H

0

0

0

0

0

FC10

FC9

FC8

00000xxx R

E685 1

USBFRAMEL

USB Frame count L

FC7

FC6

FC5

FC4

FC3

FC2

FC1

FC0

xxxxxxxx R

E686 1

MICROFRAME

Microframe count, 0-7

0

0

0

0

0

MF2

MF1

MF0

00000xxx R

E687 1

FNADDR

USB Function address

0

FA6

FA5

FA4

FA3

FA2

FA1

FA0

0xxxxxxx R

E688 2

reserved

ENDPOINTS

E68A 1

EP0BCH

Endpoint 0 Byte Count H (BC15)

(BC14)

(BC13)

(BC12)

(BC11)

(BC10)

(BC9)

(BC8)

xxxxxxxx RW

E68B 1

EP0BCL

Endpoint 0 Byte Count L (BC7)

BC6

BC5

BC4

BC3

BC2

BC1

BC0

xxxxxxxx RW

E68C 1

reserved

E68D 1

EP1OUTBC

Endpoint 1 OUT Byte

Count

0

BC6

BC5

BC4

BC3

BC2

BC1

BC0

0xxxxxxx RW

E68E 1

reserved

E68F 1

EP1INBC

Endpoint 1 IN Byte Count 0

BC6

BC5

BC4

BC3

BC2

BC1

BC0

0xxxxxxx RW

E690 1

EP2BCH

Endpoint 2 Byte Count H 0

0

0

0

0

BC10

BC9

BC8

00000xxx RW

E691 1

EP2BCL

Endpoint 2 Byte Count L BC7/SKIP

BC6

BC5

BC4

BC3

BC2

BC1

BC0

xxxxxxxx RW

E692 2

reserved

E694 1

EP4BCH

Endpoint 4 Byte Count H 0

0

0

0

0

0

BC9

BC8

000000xx RW

E695 1

EP4BCL

Endpoint 4 Byte Count L BC7/SKIP

BC6

BC5

BC4

BC3

BC2

BC1

BC0

xxxxxxxx RW

E696 2

reserved

E698 1

EP6BCH

Endpoint 6 Byte Count H 0

0

0

0

0

BC10

BC9

BC8

00000xxx RW

E699 1

EP6BCL

Endpoint 6 Byte Count L BC7/SKIP

BC6

BC5

BC4

BC3

BC2

BC1

BC0

xxxxxxxx RW

E69A 2

reserved

E69C 1

EP8BCH

Endpoint 8 Byte Count H 0

0

0

0

0

0

BC9

BC8

000000xx RW

Table 12. FX2LP Register Summary (continued)

Hex

Size Name

Description

b7

b6

b5

b4

b3

b2

b1

b0

Default

Access