Cypress Perform CY7C1561V18 User Manual

Features, Configurations, Functional description

72-Mbit QDR™-II+ SRAM 4-Word Burst

Architecture (2.5 Cycle Read Latency)

CY7C1561V18, CY7C1576V18

CY7C1563V18, CY7C1565V18

Cypress Semiconductor Corporation

•

198 Champion Court

•

San Jose

,

CA 95134-1709

•

408-943-2600

Document Number: 001-05384 Rev. *F

Revised March 6, 2008

Features

■

Separate independent read and write data ports

❐

Supports concurrent transactions

■

400 MHz clock for high bandwidth

■

4-word burst for reducing address bus frequency

■

Double Data Rate (DDR) interfaces on both read and write ports

(data transferred at 800 MHz) at 400 MHz

■

Available in 2.5 clock cycle latency

■

Two input clocks (K and K) for precise DDR timing

❐

SRAM uses rising edges only

■

Echo clocks (CQ and CQ) simplify data capture in high-speed

systems

■

Data valid pin (QVLD) to indicate valid data on the output

■

Single multiplexed address input bus latches address inputs

for both read and write ports

■

Separate port selects for depth expansion

■

Synchronous internally self-timed writes

■

Available in x8, x9, x18, and x36 configurations

■

Full data coherency, providing most current data

■

Core V

DD

= 1.8V ± 0.1V; IO V

DDQ

= 1.4V to V

DD

■

HSTL inputs and variable drive HSTL output buffers

■

Available in 165-Ball FBGA package (15 x 17 x 1.4 mm)

■

Offered in both Pb-free and non Pb-free packages

■

JTAG 1149.1 compatible test access port

■

Delay Lock Loop (DLL) for accurate data placement

Configurations

With Read Cycle Latency of 2.5 cycles:

CY7C1561V18 – 8M x 8

CY7C1576V18 – 8M x 9

CY7C1563V18 – 4M x 18

CY7C1565V18 – 2M x 36

Functional Description

The CY7C1561V18, CY7C1576V18, CY7C1563V18, and

CY7C1565V18 are 1.8V Synchronous Pipelined SRAMs,

equipped with QDR-II+ architecture. Similar to QDR-II archi-

tecture, QDR-II+ SRAMs consists of two separate ports: the read

port and the write port to access the memory array. The read port

has dedicated data outputs to support read operations and the

write port has dedicated data inputs to support write operations.

QDR-II+ architecture has separate data inputs and data outputs

to completely eliminate the need to “turn-around” the data bus

that exists with common IO devices. Each port is accessed

through a common address bus. Addresses for read and write

addresses are latched on alternate rising edges of the input (K)

clock. Accesses to the QDR-II+ read and write ports are

completely independent of one another. To maximize data

throughput, both read and write ports are equipped with DDR

interfaces. Each address location is associated with four 8-bit

words (CY7C1561V18), 9-bit words (CY7C1576V18), 18-bit

words (CY7C1563V18), or 36-bit words (CY7C1565V18) that

burst sequentially into or out of the device. Because data is trans-

ferred into and out of the device on every rising edge of both input

clocks (K and K), memory bandwidth is maximized while simpli-

fying system design by eliminating bus “turn-arounds”.

Depth expansion is accomplished with port selects, which

enables each port to operate independently.

All synchronous inputs pass through input registers controlled by

the K or K input clocks. All data outputs pass through output

registers controlled by the K or K input clocks. Writes are

conducted with on-chip synchronous self-timed write circuitry.

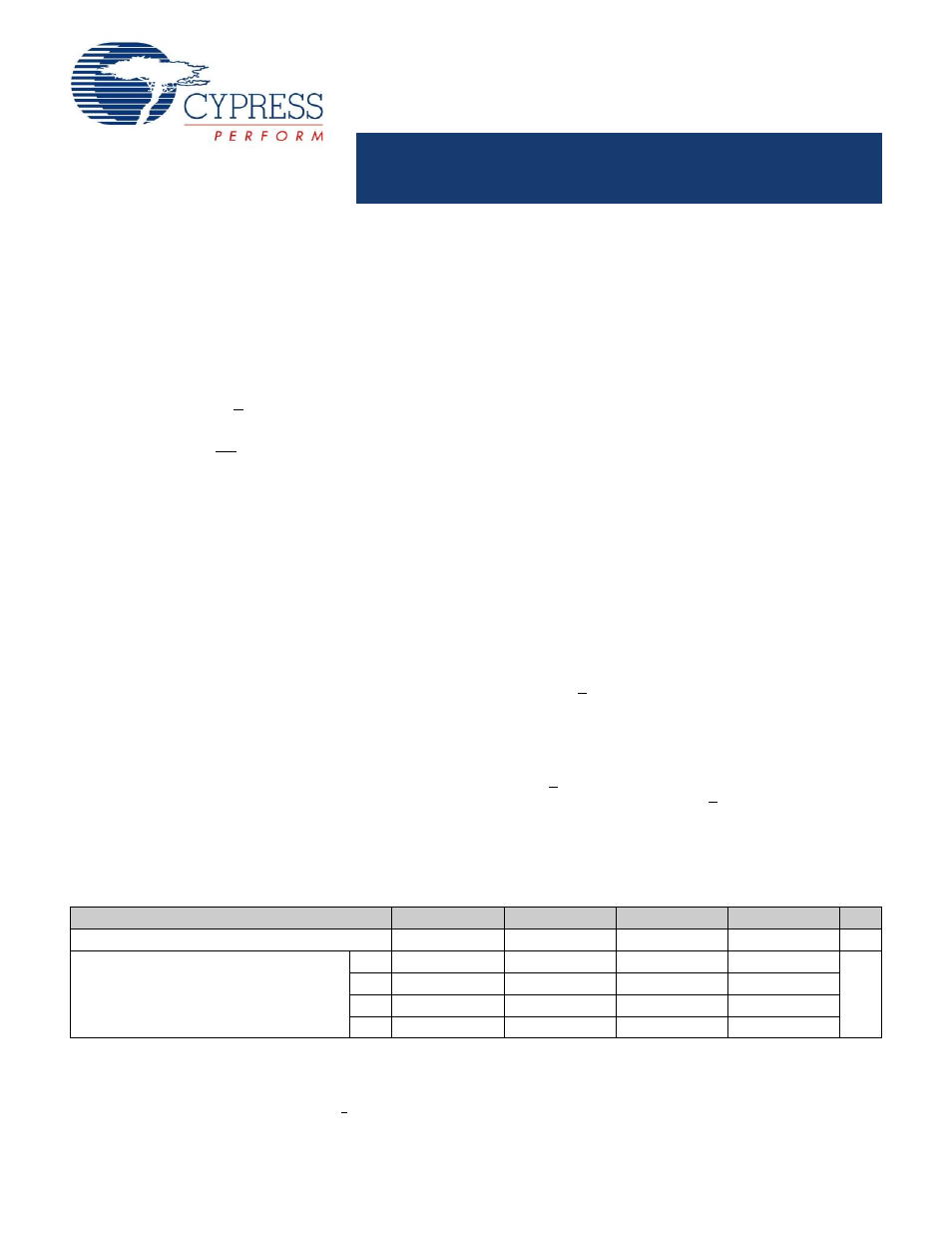

Selection Guide

Description

400 MHz

375 MHz

333 MHz

300 MHz

Unit

Maximum Operating Frequency

400

375

333

300

MHz

Maximum Operating Current

x8

1400

1300

1200

1100

mA

x9

1400

1300

1200

1100

x18

1400

1300

1200

1100

x36

1400

1300

1200

1100

Note

1. The QDR consortium specification for V

DDQ

is 1.5V + 0.1V. The Cypress QDR devices exceed the QDR consortium specification and are capable of supporting

V

DDQ

= 1.4V to V

DD

.

Document Outline

- Features

- Configurations

- Functional Description

- Selection Guide

- Logic Block Diagram (CY7C1561V18)

- Logic Block Diagram (CY7C1576V18)

- Logic Block Diagram (CY7C1563V18)

- Logic Block Diagram (CY7C1565V18)

- Pin Configuration

- Pin Definitions

- Functional Overview

- Application Example

- Write Cycle Descriptions

- Write Cycle Descriptions

- Write Cycle Descriptions

- IEEE 1149.1 Serial Boundary Scan (JTAG)

- The state diagram for the TAP controller follows. [12]

- TAP Controller State Diagram

- TAP Controller Block Diagram

- TAP Electrical Characteristics

- TAP AC Switching Characteristics

- TAP Timing and Test Conditions

- Identification Register Definitions

- Scan Register Sizes

- Instruction Codes

- Boundary Scan Order

- Power Up Sequence in QDR-II+ SRAM

- Power Up Sequence

- Maximum Ratings

- Operating Range

- Electrical Characteristics

- Capacitance

- Thermal Resistance

- Switching Characteristics

- Switching Waveforms

- Ordering Information

- Package Diagram

- Document History Page