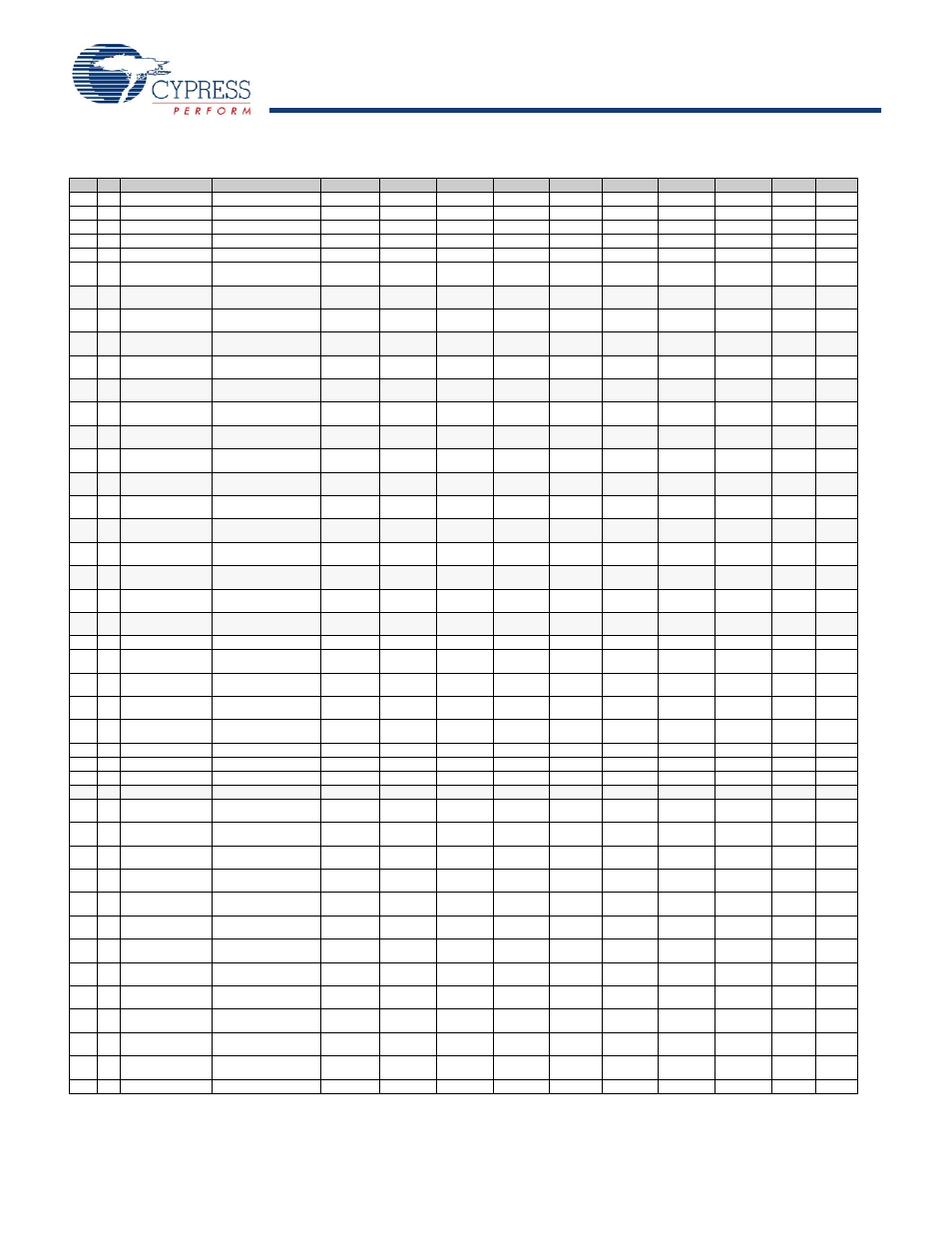

Table 12. fx2lp register summary (continued) – Cypress Perform CY7C68013 User Manual

Page 30

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

Document #: 38-08032 Rev. *L

Page 30 of 62

E62B 1

ECC1B1

ECC1 Byte 1 Address

LINE7

LINE6

LINE5

LINE4

LINE3

LINE2

LINE1

LINE0

00000000 R

E62C 1

ECC1B2

ECC1 Byte 2 Address

COL5

COL4

COL3

COL2

COL1

COL0

LINE17

LINE16

00000000 R

E62D 1

ECC2B0

ECC2 Byte 0 Address

LINE15

LINE14

LINE13

LINE12

LINE11

LINE10

LINE9

LINE8

00000000 R

E62E 1

ECC2B1

ECC2 Byte 1 Address

LINE7

LINE6

LINE5

LINE4

LINE3

LINE2

LINE1

LINE0

00000000 R

E62F 1

ECC2B2

ECC2 Byte 2 Address

COL5

COL4

COL3

COL2

COL1

COL0

0

0

00000000 R

E630

H.S.

1

EP2FIFOPFH

Endpoint 2 / slave FIFO

Programmable Flag H

DECIS

PKTSTAT

IN:PKTS[2]

OUT:PFC12

IN:PKTS[1]

OUT:PFC11

IN:PKTS[0]

OUT:PFC10

0

PFC9

PFC8

10001000 bbbbbrbb

E630

F.S.

1

EP2FIFOPFH

Endpoint 2 / slave FIFO

Programmable Flag H

DECIS

PKTSTAT

OUT:PFC12 OUT:PFC11 OUT:PFC10 0

PFC9

IN:PKTS[2]

OUT:PFC8

10001000 bbbbbrbb

E631

H.S.

1

EP2FIFOPFL

Endpoint 2 / slave FIFO

Programmable Flag L

PFC7

PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0

00000000 RW

E631

F.S

1

EP2FIFOPFL

Endpoint 2 / slave FIFO

Programmable Flag L

IN:PKTS[1]

OUT:PFC7

IN:PKTS[0]

OUT:PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0

00000000 RW

E632

H.S.

1

EP4FIFOPFH

Endpoint 4 / slave FIFO

Programmable Flag H

DECIS

PKTSTAT

0

IN: PKTS[1]

OUT:PFC10

IN: PKTS[0]

OUT:PFC9

0

0

PFC8

10001000 bbrbbrrb

E632

F.S

1

EP4FIFOPFH

Endpoint 4 / slave FIFO

Programmable Flag H

DECIS

PKTSTAT

0

OUT:PFC10 OUT:PFC9 0

0

PFC8

10001000 bbrbbrrb

E633

H.S.

1

EP4FIFOPFL

Endpoint 4 / slave FIFO

Programmable Flag L

PFC7

PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0

00000000 RW

E633

F.S

1

EP4FIFOPFL

Endpoint 4 / slave FIFO

Programmable Flag L

IN: PKTS[1]

OUT:PFC7

IN: PKTS[0]

OUT:PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0

00000000 RW

E634

H.S.

1

EP6FIFOPFH

Endpoint 6 / slave FIFO

Programmable Flag H

DECIS

PKTSTAT

IN:PKTS[2]

OUT:PFC12

IN:PKTS[1]

OUT:PFC11

IN:PKTS[0]

OUT:PFC10

0

PFC9

PFC8

00001000 bbbbbrbb

E634

F.S

1

EP6FIFOPFH

Endpoint 6 / slave FIFO

Programmable Flag H

DECIS

PKTSTAT

OUT:PFC12 OUT:PFC11 OUT:PFC10 0

PFC9

IN:PKTS[2]

OUT:PFC8

00001000 bbbbbrbb

E635

H.S.

1

EP6FIFOPFL

Endpoint 6 / slave FIFO

Programmable Flag L

PFC7

PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0

00000000 RW

E635

F.S

1

EP6FIFOPFL

Endpoint 6 / slave FIFO

Programmable Flag L

IN:PKTS[1]

OUT:PFC7

IN:PKTS[0]

OUT:PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0

00000000 RW

E636

H.S.

1

EP8FIFOPFH

Endpoint 8 / slave FIFO

Programmable Flag H

DECIS

PKTSTAT

0

IN: PKTS[1]

OUT:PFC10

IN: PKTS[0]

OUT:PFC9

0

0

PFC8

00001000 bbrbbrrb

E636

F.S

1

EP8FIFOPFH

Endpoint 8 / slave FIFO

Programmable Flag H

DECIS

PKTSTAT

0

OUT:PFC10 OUT:PFC9 0

0

PFC8

00001000 bbrbbrrb

E637

H.S.

1

EP8FIFOPFL

Endpoint 8 / slave FIFO

Programmable Flag L

PFC7

PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0

00000000 RW

E637

F.S

1

EP8FIFOPFL

Endpoint 8 / slave FIFO

Programmable Flag L

IN: PKTS[1]

OUT:PFC7

IN: PKTS[0]

OUT:PFC6

PFC5

PFC4

PFC3

PFC2

PFC1

PFC0

00000000 RW

8

reserved

E640 1

EP2ISOINPKTS

EP2 (if ISO) IN Packets

per frame (1-3)

AADJ

0

0

0

0

0

INPPF1

INPPF0

00000001 brrrrrbb

E641 1

EP4ISOINPKTS

EP4 (if ISO) IN Packets

per frame (1-3)

AADJ

0

0

0

0

0

INPPF1

INPPF0

00000001 brrrrrrr

E642 1

EP6ISOINPKTS

EP6 (if ISO) IN Packets

per frame (1-3)

AADJ

0

0

0

0

0

INPPF1

INPPF0

00000001 brrrrrbb

E643 1

EP8ISOINPKTS

EP8 (if ISO) IN Packets

per frame (1-3)

AADJ

0

0

0

0

0

INPPF1

INPPF0

00000001 brrrrrrr

E644 4

reserved

E648 1

INPKTEND

[11]

Force IN Packet End

Skip

0

0

0

EP3

EP2

EP1

EP0

xxxxxxxx W

E649 7

OUTPKTEND

Force OUT Packet End

Skip

0

0

0

EP3

EP2

EP1

EP0

xxxxxxxx W

INTERRUPTS

E650 1

EP2FIFOIE

Endpoint 2 slave FIFO

Flag Interrupt Enable

0

0

0

0

EDGEPF

PF

EF

FF

00000000 RW

E651 1

EP2FIFOIRQ

Endpoint 2 slave FIFO

Flag Interrupt Request

0

0

0

0

0

PF

EF

FF

00000000 rrrrrbbb

E652 1

EP4FIFOIE

Endpoint 4 slave FIFO

Flag Interrupt Enable

0

0

0

0

EDGEPF

PF

EF

FF

00000000 RW

E653 1

EP4FIFOIRQ

Endpoint 4 slave FIFO

Flag Interrupt Request

0

0

0

0

0

PF

EF

FF

00000000 rrrrrbbb

E654 1

EP6FIFOIE

Endpoint 6 slave FIFO

Flag Interrupt Enable

0

0

0

0

EDGEPF

PF

EF

FF

00000000 RW

E655 1

EP6FIFOIRQ

Endpoint 6 slave FIFO

Flag Interrupt Request

0

0

0

0

0

PF

EF

FF

00000000 rrrrrbbb

E656 1

EP8FIFOIE

Endpoint 8 slave FIFO

Flag Interrupt Enable

0

0

0

0

EDGEPF

PF

EF

FF

00000000 RW

E657 1

EP8FIFOIRQ

Endpoint 8 slave FIFO

Flag Interrupt Request

0

0

0

0

0

PF

EF

FF

00000000 rrrrrbbb

E658 1

IBNIE

IN-BULK-NAK Interrupt

Enable

0

0

EP8

EP6

EP4

EP2

EP1

EP0

00000000 RW

E659 1

IBNIRQ

IN-BULK-NAK interrupt

Request

0

0

EP8

EP6

EP4

EP2

EP1

EP0

00xxxxxx rrbbbbbb

E65A 1

NAKIE

Endpoint Ping-NAK / IBN

Interrupt Enable

EP8

EP6

EP4

EP2

EP1

EP0

0

IBN

00000000 RW

E65B 1

NAKIRQ

Endpoint Ping-NAK / IBN

Interrupt Request

EP8

EP6

EP4

EP2

EP1

EP0

0

IBN

xxxxxx0x bbbbbbrb

E65C 1

USBIE

USB Int Enables

0

EP0ACK

HSGRANT

URES

SUSP

SUTOK

SOF

SUDAV

00000000 RW

Note

12. The register can only be reset, it cannot be set.

Table 12. FX2LP Register Summary (continued)

Hex

Size Name

Description

b7

b6

b5

b4

b3

b2

b1

b0

Default

Access