Table 6. clocks to adc, 4 cs8406 control (address 04h), Table 7. data to cs8406 – Cirrus Logic CDB42448 User Manual

Page 19: Table 6. clocks to adc table 7. data to cs8406, P 19

CDB42448

DS648DB2

19

5.3.3

ADC MUX (ADC.CLK_MUX)

Default = 11

Function:

This MUX selects the sub-clock lines from the CS8416, DAC, DSP Header and the sub-clocks from

the TDMer internal to the FPGA (see Figure 3 on page 10).

5.3.4

FPGA CLOCKS TO ADC CLOCKS (FPGA->ADC)

Default = 0

0 - FPGA Masters ADC clock bus

1 - FPGA Slave to ADC clock bus

Function:

This bit toggles a control line for the internal clock buffer to the ADC serial port (see Figure 3 on page

10).

5.4

CS8406 CONTROL (ADDRESS 04H)

5.4.1

RESET (RST)

Default = 1

0 - CS8406 held in reset

1 - CS8406 taken out of reset

Function:

This bit is used to reset the CS8406 and is held low for 300

µs upon FPGA initialization.

5.4.2

DATA MUX(MUX)

Default = 100

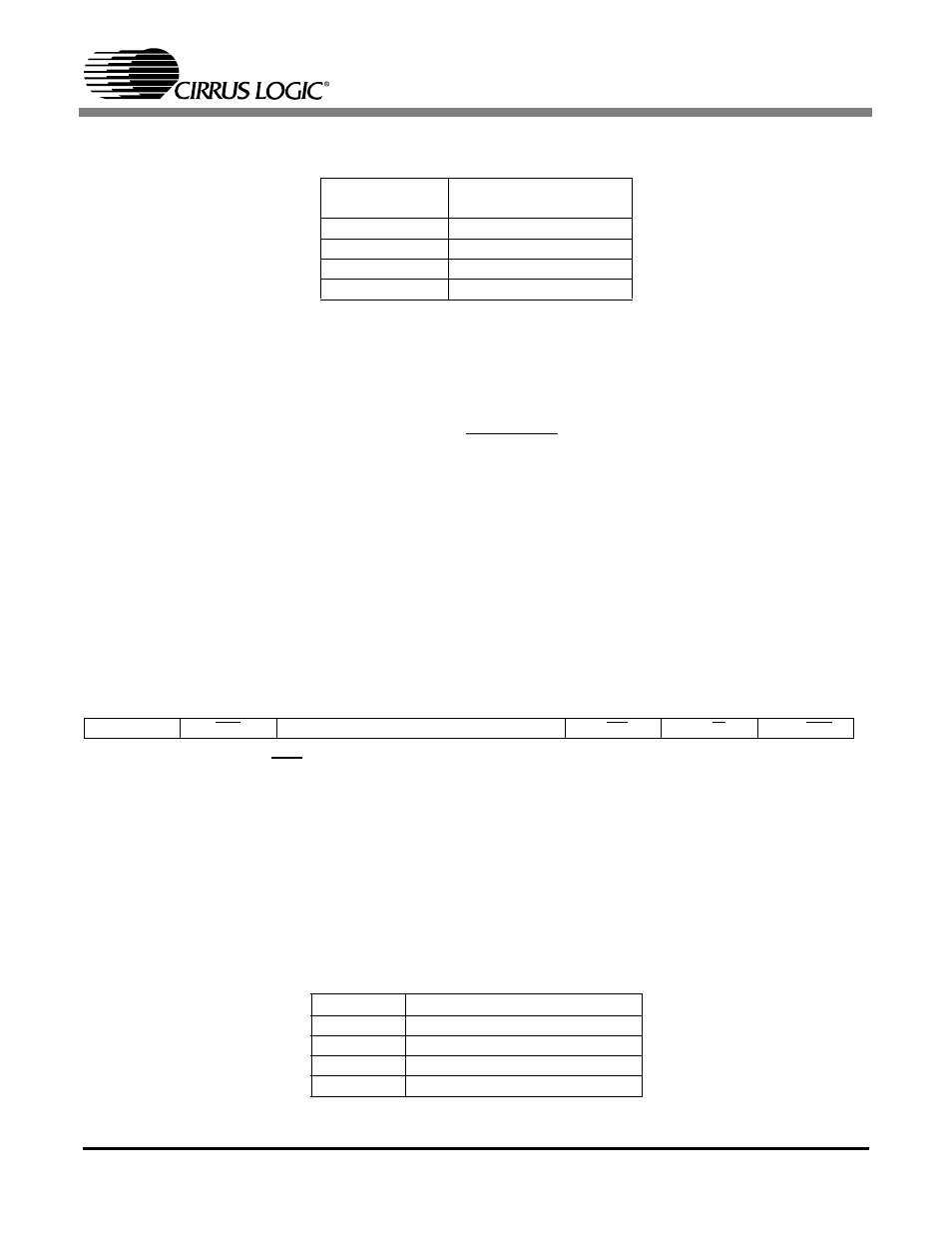

ADC.CLK_

MUX[1:0]

Clock Selection

00

CS8416

01

DAC

10

DSP ADC

11

TDMer

Table 6. Clocks to ADC

7

6

5

4

3

2

1

0

Reserved

RST

MUX2

MUX1

MUX0

128/256 Fs

I²S/LJ

T2P/ADC

MUX[2:0]

Data Selection

000

ADC_SDOUT

001

ADC_SDOUT2

010

ADC_SDOUT3

011

ADC_SDOUT1

Table 7. Data to CS8406