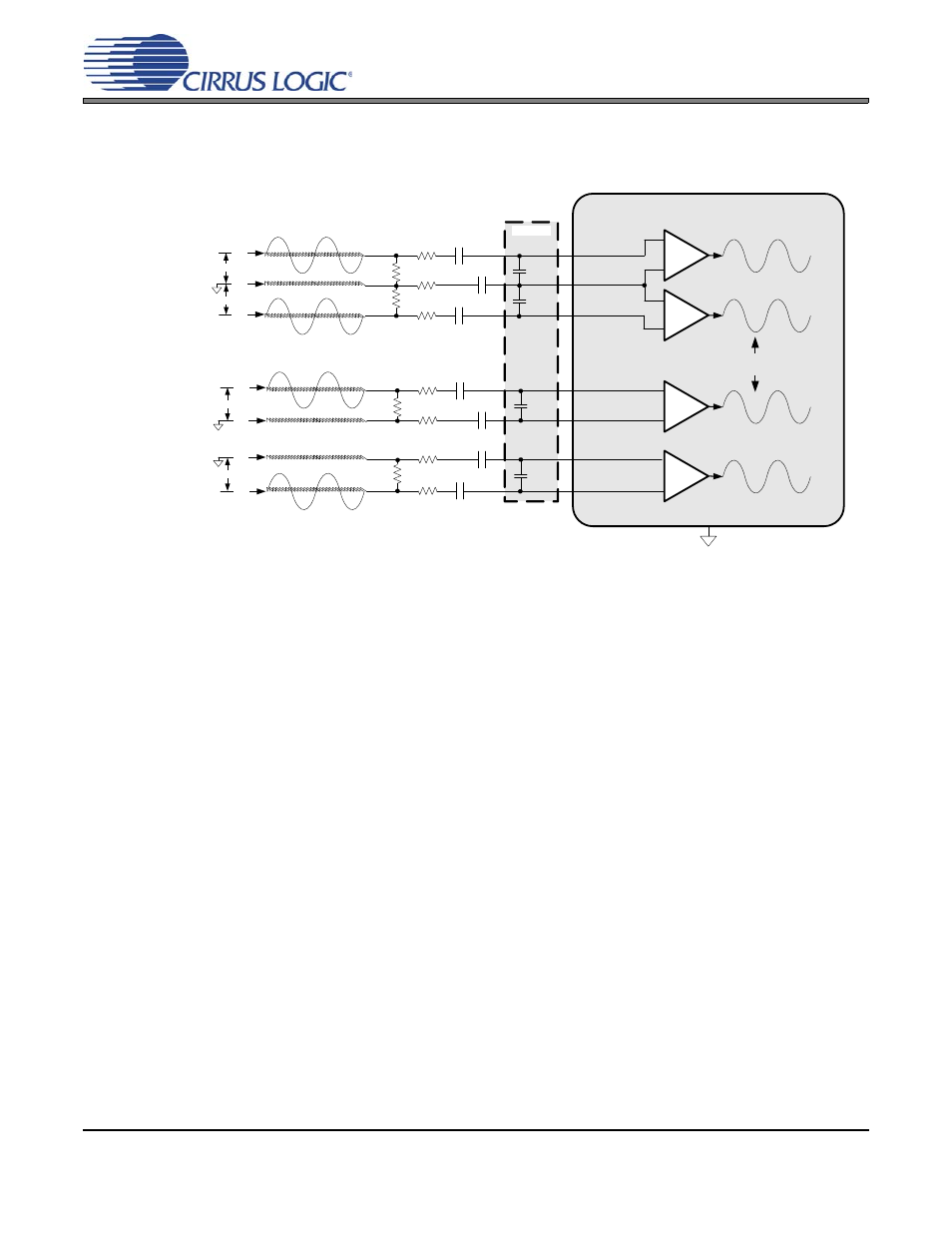

Figure 12.pseudo-differential input filter, Cs4207, Figure 12. pseudo-differential input filter – Cirrus Logic CS4207 User Manual

Page 140

140

DS880F4

CS4207

For an improvement from using the single-ended circuitry, both analog stereo input pairs may be configured

in a pseudo-differential topology. This provides common-mode noise rejection for single-ended inputs by

differentially routing LINEIN_C-, MICIN_L-, and/or MICIN_R- with the signal traces. See

for the

recommended pseudo-differential input filter.

LINEIN_L+

1800 pF

1800 pF

100 k

100

LINEIN_R+

*

*

1 µF

1 µF

100 k

100

NPO/C0G dielectric capacitors.

Note:

1. These capacitors serve as a charge reservoir for the internal switched capacitor ADC

modulators and should be placed as close as possible to the inputs.

Note 1

*

Low ESR, X7R/X5R dielectric capacitors.

**

**

**

MICIN_L+

1800 pF

1800 pF

100 k

100

MICIN_R+

*

*

1 µF

1 µF

100 k

100

**

**

LINEIN_C-

MICIN_L-

MICIN_R-

CS4207

1 µF

**

100

100

100

1 µF

**

1 µF

**

common mode rejection at input of PGA

reduces external system noise

//

//

Right Analog Input 2

GND

(differential traces )

//

//

Left Analog Input 1

GND

(differential traces )

//

Right Analog Input 1

(differential traces )

//

//

Left Analog Input 2

GND

(differential traces )

+

-

PGA

-

+

PGA

+

-

PGA

-

+

PGA

AGND

Figure 12. Pseudo-Differential Input Filter