3 adc configuration (cir = 0002h), Adc configuration (cir = 0002h), Cs4207 – Cirrus Logic CS4207 User Manual

Page 131

DS880F4

131

CS4207

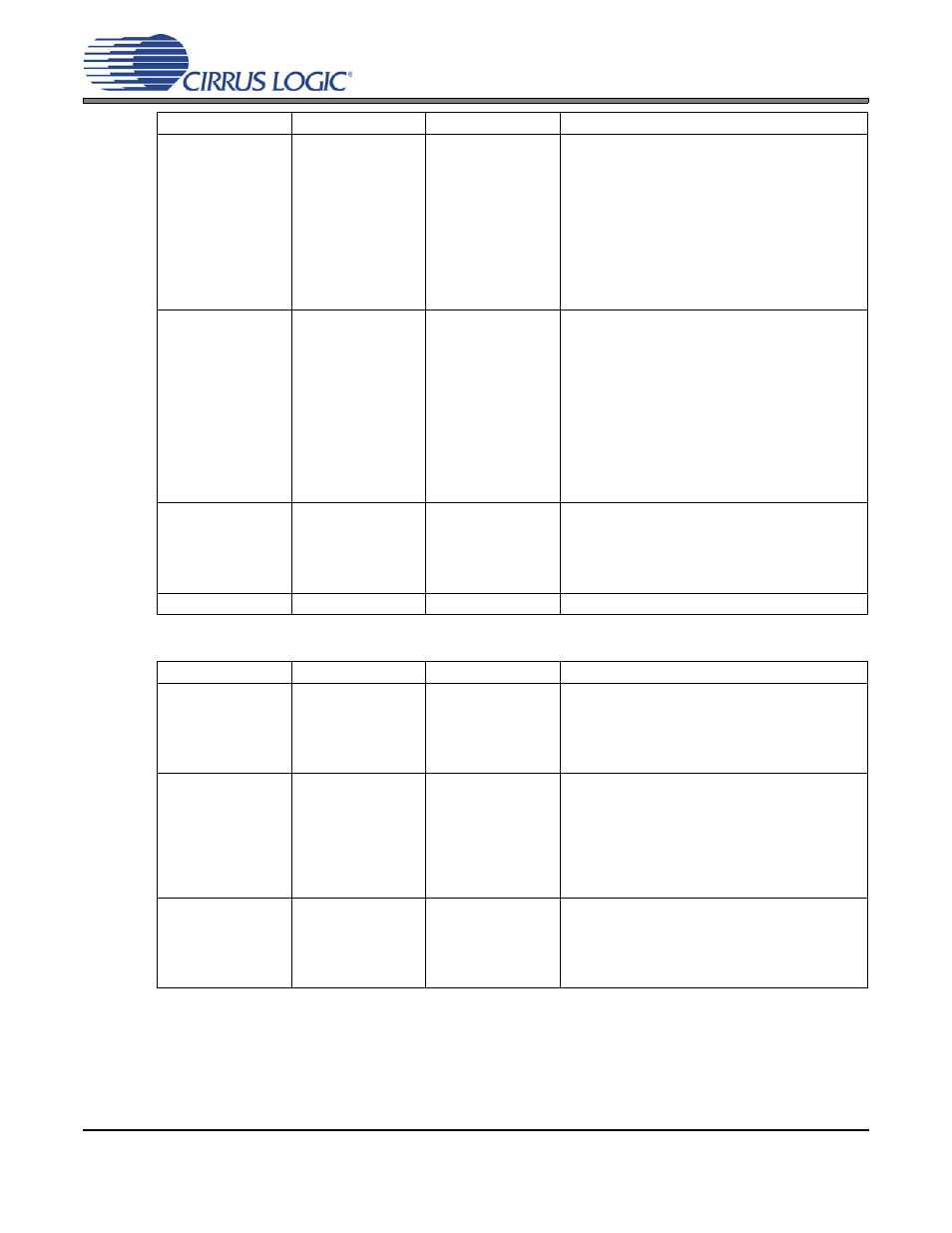

6.15.6.3 ADC Configuration (CIR = 0002h)

4:3

Read/Write

01b

HOLD[1:0] – Determines how received AES3

audio sample is affected when an receive error

occurs. The errors that affect hold behavior are

parity, bi-phase and confidence. HOLD has no

effect in Raw S/PDIF RX Data Mode.

00 - hold last audio sample.

01 - replace the current audio sample with all

zeros (mute).

10 - do not change the received audio sample.

11 - reserved

2

Read/Write

0b

TRUNC – Determines if the audio word length is

set according to the incoming channel status

data as decoded by the AUX[3:0] bits. The

resulting word length in bits is 24 minus

AUX[3:0]. The TRUNC function is valid only on

PCM audio data.

0 – Incoming data is not truncated.

1 – Incoming data is truncated according to the

length specified in the channel status data.

TRUNC has no effect on output data if detected

as being non-audio.

1

Read/Write

0b

SRC_MUTE – When SRC_MUTE is set to ‘1’,

the SRC will soft-mute when it loses lock and soft

unmute when it regains lock.

0 - Soft mute disabled

1 - Soft mute enabled

0

Read/Write

0b

Reserved

Bits

Type

Default

Description

15

Read/Write

0b

URG (Unsolicited Response Gating): This bit

allows unsolicited responses to be gated.

0 - Normal propagation of unsolicited responses.

1 - Unsolicited responses are gated if AFG is in

D3.

14

Read/Write

0b

ADC2 Gain: This bit adjusts the gain of the Mic

In 1/Line In 2 path for the given input topology.

0 - 6 dB gain added (pseudo-differential and sin-

gle-ended mode).

1 - no gain added (fully differential mode).

Note: This bit is OR’ed with the BTL bit in the

In 1/Line In 2 EAPD/BTL Enable

Control.

13

Read/Write

0b

ADC1 Gain: This bit adjusts the gain of the Line

In 1/Mic In 2 path for the given input topology.

0 - 6 dB gain added (pseudo-differential and sin-

gle-ended mode).

1 - no gain added (not supported - test only).

Bits

Type

Default

Description