Cirrus Logic CS4207 User Manual

Cs4207, Digital to analog features, Analog to digital features

Copyright Cirrus Logic, Inc. 2012

(All Rights Reserved)

AUG '12

DS880F4

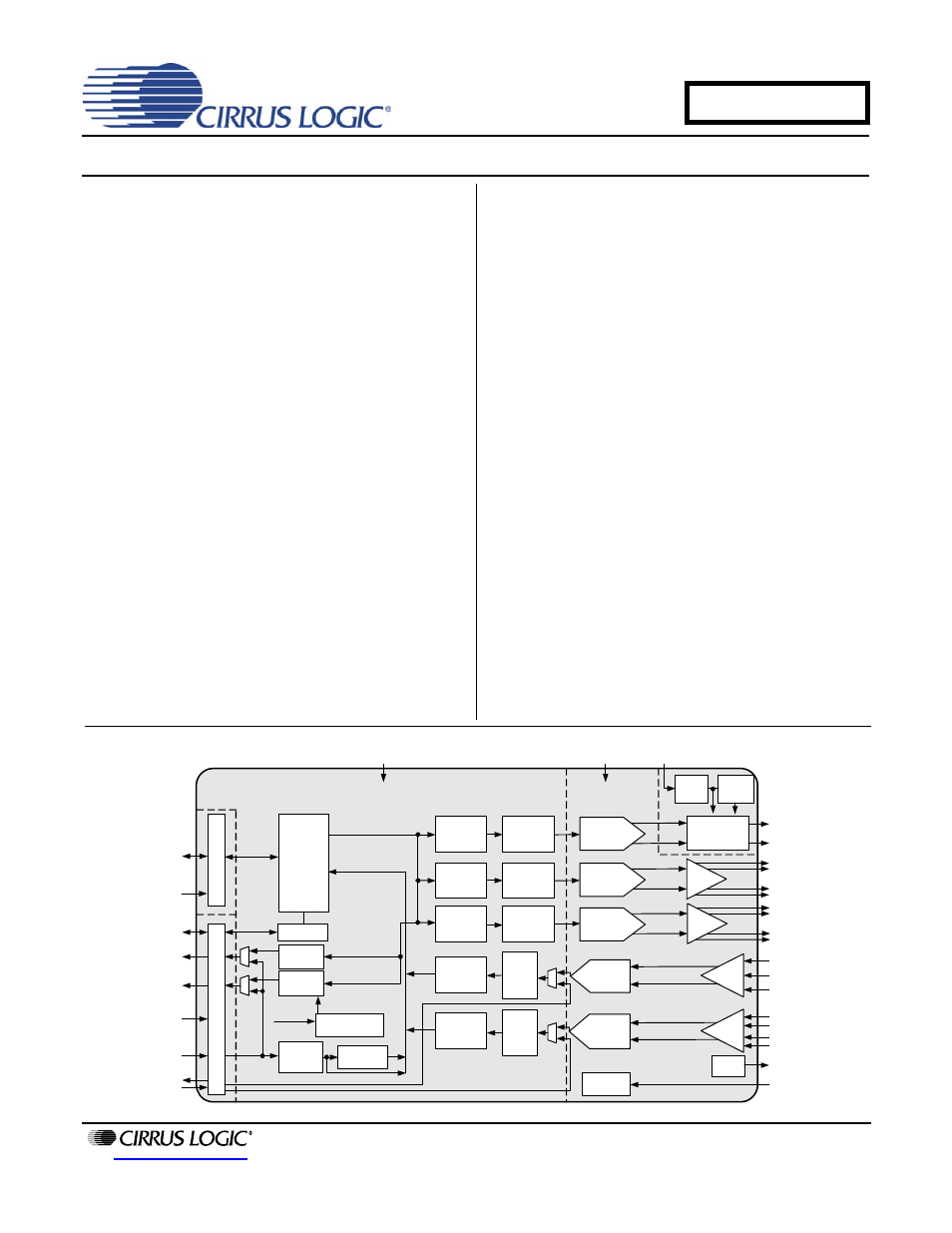

Low-power, 4-in / 6-out HD Audio Codec with Headphone Amp

DIGITAL to ANALOG FEATURES

DAC1 (Headphone)

–

101 dB Dynamic Range (A-wtd)

–

-89 dB THD+N

Headphone Amplifier - GND Centered

–

Integrated Negative-voltage Regulator

–

No DC-blocking Capacitor Required

–

50 mW Power/Channel into 16

DAC2 & DAC3 (Line Outs)

–

110 dB Dynamic Range (A-wtd)

–

-94 dB THD+N

–

Differential Balanced or Single-ended

Each DAC Supports 32 kHz to 192 kHz Sample

Rates Independently.

Digital Volume Control

–

+6.0 dB to -57.5 dB in 0.5 dB Steps

–

Zero Cross and/or Soft Ramp Transitions

Independent Support of D0 and D3 Power

States for Each DAC

Fast D3 to D0 Transition

–

Audio Playback in Less Than 50 ms

ANALOG to DIGITAL FEATURES

ADC1 & ADC2

–

105 dB Dynamic Range (A-wtd)

–

-88 dB THD+N

–

Differential Balanced or Single-ended

Inputs

–

Analog Programmable Gain Amplifier

(PGA) ±12 dB, 1.0 dB Steps, with Zero

Cross Transitions and Mute

MIC Inputs

–

Pre-amplifier with Selectable 0 dB, +10 dB,

+20 dB, and +30 dB Gain Settings

–

Programmable, Low-noise MIC Bias Level

Each ADC Supports 8 kHz to 96 kHz Sample

Rates Independently

Additional Digital Attenuation Control

–

-13.0 dB to -51.0 dB in 1.0 dB steps

–

Zero Cross and/or Soft Ramp Transitions

Digital Interface for Two Dual Digital Mic Inputs

Independent Support of D0 and D3 Power

States for Each ADC

VL_HD

(1.5 V to 3.3 V)

SRC &

Multibit

Modulator

Chrg

Pump

Invert

Left HP Out

Left Line Out

2-Chnl

ADC1

Le

v

e

l T

ra

n

sl

at

o

r

HD Audio

Bus

Line/Mic In L

Line/Mic In R

Headphone

Amp - GND

Centered

MIC

Bias

2-Chnl

DAC1

Line

Out

+

-

Right Line Out

+

-

Left Line Out

Line

Out

+

-

Right Line Out

+

-

+

-

+

PGA

Digital

Filter &

SRC

2-Chnl

ADC2

Mic/Line In L

Mic/Line In R

+

-

+

-

PGA

Digital

Filter &

SRC

D-Mic Clock

SPDIF

TX 1

SPDIF

RX SRC

S/PDIF OUT 1

S/PDIF IN

GPIO

GPIO

Right HP Out

D-Mic In

HD

Audio

Interface

Chrg

Pump

Buck

+VHP

-VHP

2-Chnl

DAC2

2-Chnl

DAC3

SRC &

Multibit

Modulator

SRC &

Multibit

Modulator

VD

(1.5 V to 1.8 V)

Vol/Mute

Vol/Mute

Vol/Mute

Vol/Boost/

Mute

Vol/Boost/

Mute

VA, VA_REF

(3.3 V to 5.0 V)

VA_HP

(3.3 V to 5.0 V)

Mic Bias

Leve

l T

ra

n

slat

o

r

VL_IF

(3.3 V)

Jack

Sense

SENSE_A

SPDIF

TX 2

S/PDIF OUT 2

128Fs Clock

Multiplier

HD Bus

Fs

SPDIF

RX

CS4207

Document Outline

- Table of Contents

- List of Figures

- List of Tables

- 1. Pin Descriptions

- 2. Typical Connection Diagrams

- 3. Characteristics and Specifications

- Recommended Operating Conditions

- Absolute Maximum Ratings

- Analog Input Characteristics (Commercial - CNZ)

- Analog Input Characteristics (Automotive - DNZ)

- ADC Digital Filter Characteristics

- Analog Output Characteristics (Commercial - CNZ)

- Analog Output Characteristics (Automotive - DNZ)

- Combined DAC Interpolation & on-Chip Analog FIlter Response

- DC Electrical Characteristics

- Digital Microphone Interface Characteristics

- Digital Interface Specifications & Characteristics

- HD Audio Bus Specifications & Characteristics

- S/PDIF Transmitter/Receiver Specifications & Characteristics

- Power Consumption

- 4. Codec Reset and Initialization

- 5. Presence Detection

- 6. HD Audio Codec Supported Verbs and Responses

- 6.1 Software Programming Model

- 6.2 Root Node (Node ID = 00h)

- 6.3 Audio Function Group (Node ID = 01h)

- 6.3.1 Subordinate Node Count

- 6.3.2 Function Group Type

- 6.3.3 Audio Function Group Capabilities

- 6.3.4 Supported PCM Size, Rates

- 6.3.5 Supported Stream Formats

- 6.3.6 Supported Power States

- 6.3.7 GPIO Capabilities

- 6.3.8 Power States

- 6.3.9 GPIO Data

- 6.3.10 GPIO Enable Mask

- 6.3.11 GPIO Direction

- 6.3.12 GPIO Sticky Mask

- 6.3.13 Implementation Identification

- 6.3.14 Function Reset

- 6.4 DAC1, DAC2, DAC3 Output Converter Widgets (Node ID = 02h, 03h, 04h)

- 6.5 ADC1, ADC2 Input Converter Widgets (Node ID = 05h, 06h)

- 6.5.1 Audio Widget Capabilities

- 6.5.2 Supported PCM Size, Rates

- 6.5.3 Supported Stream Formats

- 6.5.4 Input Amplifier Capabilities

- 6.5.5 Connection List Length

- 6.5.6 Supported Power States

- 6.5.7 ADC1 Connection List Entry

- 6.5.8 ADC1 Connection Select Control

- 6.5.9 ADC2 Connection List Entry

- 6.5.10 ADC2 Connection Select Control

- 6.5.11 Power States

- 6.5.12 Converter Stream, Channel

- 6.5.13 Converter Format

- 6.5.14 Amplifier Gain/Mute

- 6.6 S/PDIF Receiver Input Converter Widget (Node ID = 07h)

- 6.7 S/PDIF Transmitter 1, S/PDIF Transmitter 2 Output Converter Widgets (Node ID = 08h, 14h)

- 6.8 Headphone Pin Widget (Node ID = 09h)

- 6.9 Line Out 1 Pin Widget (Node ID = 0Ah)

- 6.10 Line Out 2 Pin Widget (Node ID = 0Bh)

- 6.11 Line In 1/Mic In 2, Mic In 1/Line In 2 Pin Widgets (Node ID = 0Ch, 0Dh)

- 6.11.1 Audio Widget Capabilities

- 6.11.2 Line In 1/Mic In 2 Pin Capabilities

- 6.11.3 Mic In 1/Line In 2 Pin Capabilities

- 6.11.4 Input Amplifier Capabilities

- 6.11.5 Supported Power States

- 6.11.6 Power States

- 6.11.7 Line In 1/Mic In 2 Pin Widget Control

- 6.11.8 Mic In 1/Line In 2 Pin Widget Control

- 6.11.9 Unsolicited Response Control

- 6.11.10 Pin Sense

- 6.11.11 Mic In 1/Line In 2 EAPD/BTL Enable

- 6.11.12 Line In 1/Mic In 2 Configuration Default

- 6.11.13 Mic In 1/Line In 2 Configuration Default

- 6.11.14 Amplifier Gain/Mute

- 6.12 Digital Mic In 1, Digital Mic In 2 Pin Widgets (Node ID = 0Eh, 12h)

- 6.13 S/PDIF Receiver Input Pin Widget (Node ID = 0Fh)

- 6.14 S/PDIF Transmitter 1, S/PDIF Transmitter 2 Output Pin Widgets (Node ID = 10h, 15h)

- 6.14.1 Audio Widget Capabilities

- 6.14.2 Pin Capabilities

- 6.14.3 Connection List Length

- 6.14.4 S/PDIF Transmitter 1 Connection List Entry

- 6.14.5 S/PDIF Transmitter 2 Connection List Entry

- 6.14.6 Pin Widget Control

- 6.14.7 S/PDIF Transmitter 1 Configuration Default

- 6.14.8 S/PDIF Transmitter 2 Configuration Default

- 6.15 Vendor Processing Widget (Node ID = 11h)

- 6.16 Beep Generator Widget (Node ID = 13h)

- 7. Applications

- 8. PCB Layout Considerations

- 9. Parameter Definitions

- 10. QFN Package Dimensions

- 11. Ordering Information

- 12. References

- 13. Revision History