Cs4207 – Cirrus Logic CS4207 User Manual

Page 132

132

DS880F4

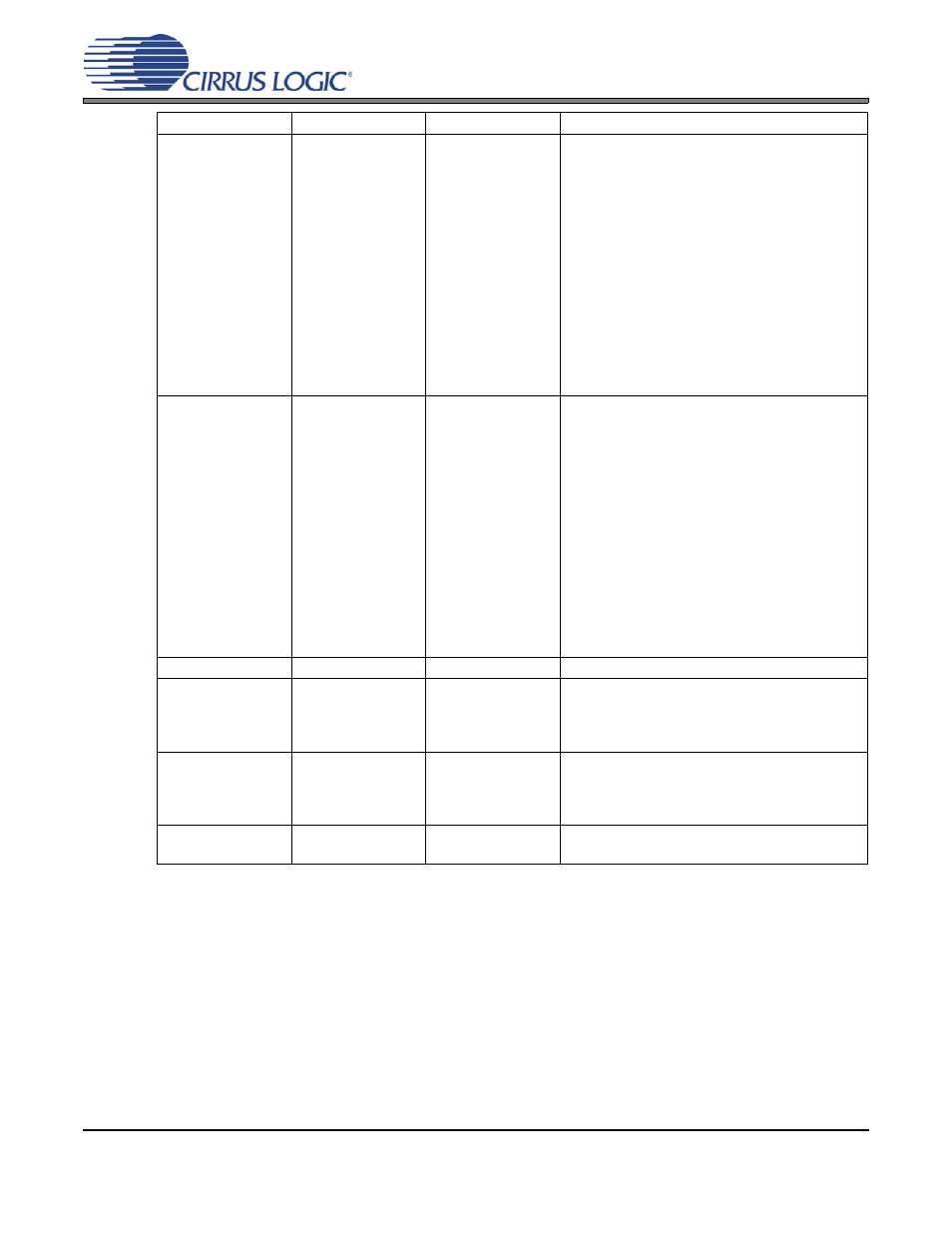

CS4207

12:11

Read/Write

00b

ADC2 Channel Mode[1:0]: Controls the chan-

nel mapping from the ADC2 output to the HDA

bus.

‘00’b - ADC2 left channel is mapped to HDA left

channel and ADC2 right channel is mapped HDA

right channel (normal mode).

‘01’b - ADC2 left channel is mapped to both HDA

left and right channels. ADC2 right channel is

discarded (mono mode).

‘10’b - ADC2 right channel is mapped to both

HDA left and right channels. ADC2 left channel is

discarded (alternate mono mode).

‘11’b - ADC2 left channel is mapped to HDA right

channel and ADC2 right channel is mapped to

HDA left channel (channel swap mode).

10:9

Read/Write

00b

ADC1 Channel Mode[1:0]: Controls the chan-

nel mapping from the ADC1 output to the HDA

bus.

‘00’b - ADC1 left channel is mapped to HDA left

channel and ADC1 right channel is mapped HDA

right channel (normal mode).

‘01’b - ADC1 left channel is mapped to both HDA

left and right channels. ADC1 right channel is

discarded (mono mode).

‘10’b - ADC1 right channel is mapped to both

HDA left and right channels. ADC1 left channel is

discarded (alternate mono mode).

‘11’b - ADC1 left channel is mapped to HDA right

channel and ADC1 right channel is mapped to

HDA left channel (channel swap mode).

8:6

Read/Write

000b

Reserved

5

Read/Write

0b

ADC2 PGA Mode: Sets the topology for the Mic

In 1/Line In 2 PGA.

0 - Fully differential or pseudo-differential mode.

1 - Single-ended mode.

4

Read/Write

0b

ADC1 PGA Mode: Sets the topology for the Line

In 1/Mic In 2 PGA.

0 - Pseudo-differential mode.

1 - Single-ended mode.

3:2

Read/Write

10b

ADC2 SZCMode[1:0]: Same function as ADC1.

See below.

Bits

Type

Default

Description