E. determine the flyback nominal timing t1 and t2, An368 – Cirrus Logic AN368 User Manual

Page 15

AN368

AN368REV2

15

The minimum switching frequency F

sw(min)

for the second stage is configured to provide good power

regulation. The minimum switching frequency should be set to the smallest possible value, but it should remain

outside of the audible frequency range. F

sw(min)

is configured using register TTMAX at Address 38. Bits

TTMAX[7:0] set the maximum allowable target period for the second-stage time TT:

The maximum second-stage switching period that is measured by the controller algorithm is set using bits

TT_MAX[1:0] in register Config3 at Address 35.

There are two modes of operation, and the output configuration in each of these modes is different.

Mode 1: Switching Event TT

CH1

In Mode 1 the phase synchronizer FET Q3 is switched ‘OFF’. Output voltage V

MODE1

and output current

I

MODE1

are calculated using Equations 7 and 8, respectively:

where,

V

CH1

= Channel 1 secondary output VDC (channel 1 LED string supply voltage)

V

CH2

= Channel 2 secondary output VDC (channel 2 LED string supply voltage)

V

D15

= Forward bias voltage across diode D15

V

D5

= Forward bias voltage across diode D5

I

CH2

= Channel 2 LED current

Mode 2: Switching Event TT

CH2

In Mode 2, phase synchronizer MOSFET Q3 is switched ‘ON’. Output voltage V

MODE2

and output current

I

MODE2

are calculated using Equations 9 and 10, respectively:

where,

I

CH1

= Channel 1 LED current

e. Determine the Flyback Nominal Timing T1 and T2

Assume that the power transferred in Mode 1 is greater than the power transferred in Mode 2. Select a Mode 1

switching frequency F

sw1

for optimal driver performance using the criteria described above.

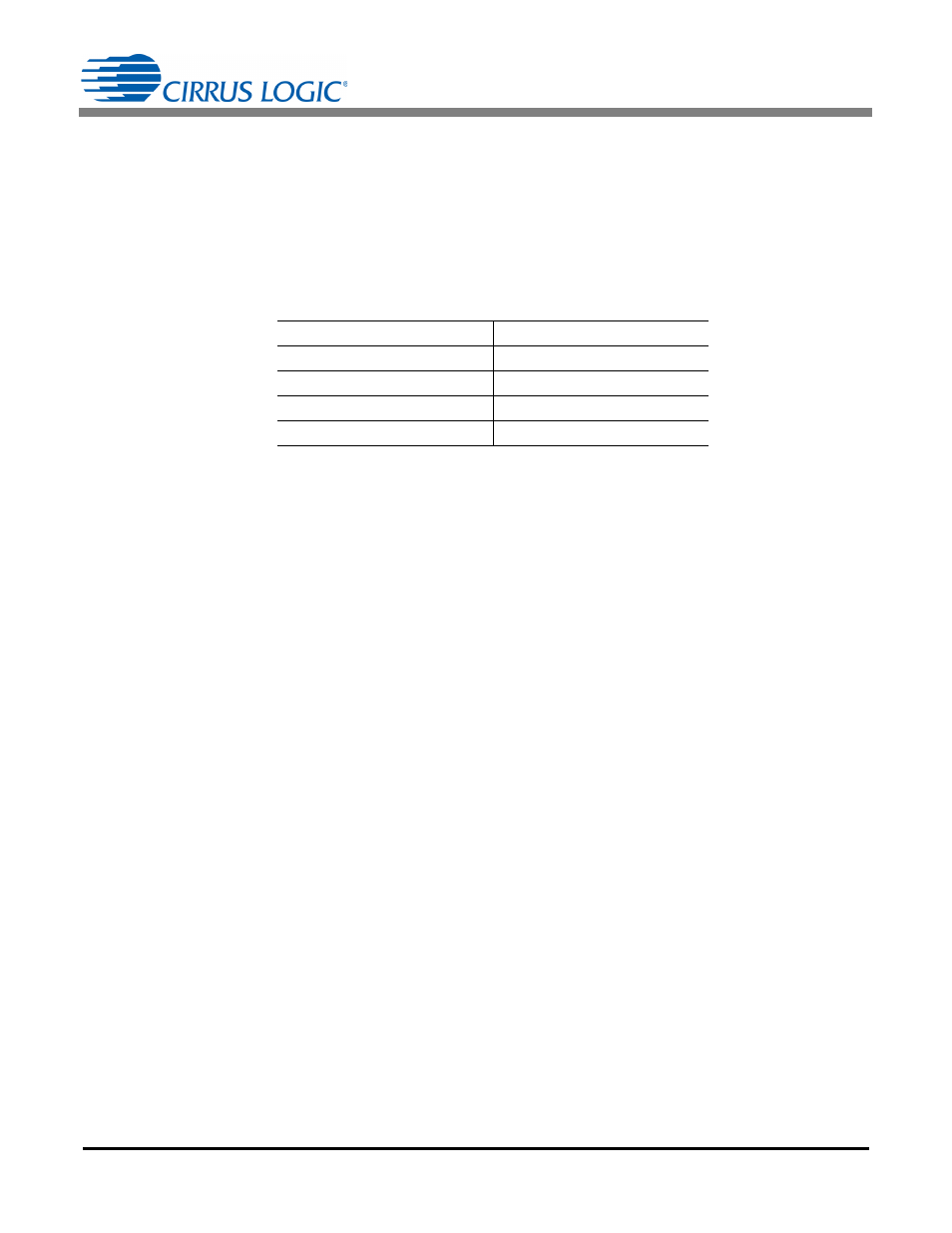

TT_MAX[1:0]

Max Switching Period

0

51.15

s

1

102.35

s

2

153.55

s

3

204.75

s

Table 1. Maximum Measurable Switching Period

1

F

sw min

--------------------

TTMAX[7:0] 128 127

+

50ns

=

[Eq. 6]

V

MODE1

V

CH1

V

CH2

V

D15

V

D5

+

+

+

=

[Eq. 7]

I

MODE1

I

CH2

=

[Eq. 8]

V

MODE2

V

CH1

V

D15

+

=

[Eq. 9]

I

MODE2

I

CH1

I

CH2

–

=

[Eq. 10]