6 extended control register (base + 402h) – B&B Electronics SPP-100 - Manual User Manual

Page 53

8.2.5 EPP Data Registers 0-3 (Base + 4 through Base + 7)

These registers are only available in EPP mode. Writing any one of these

registers will initiate an EPP Data Write Cycle, and reading any one of

these registers will initiate an EPP Data Read Cycle. These four addresses

all access the same 8-bit register. This is useful in that it will allow the

CPU to do 8,16, or 32 bit data writes to the port.

8.2.6 Extended Control Register (Base + 402h)

The Extended Control Register (Present only in Revision E and earlier

PCMCIA Cards) is used to set the mode of the SPP-100 parallel port. The

upper three bits (7:5) are written to configure the appropriate parallel port

mode.

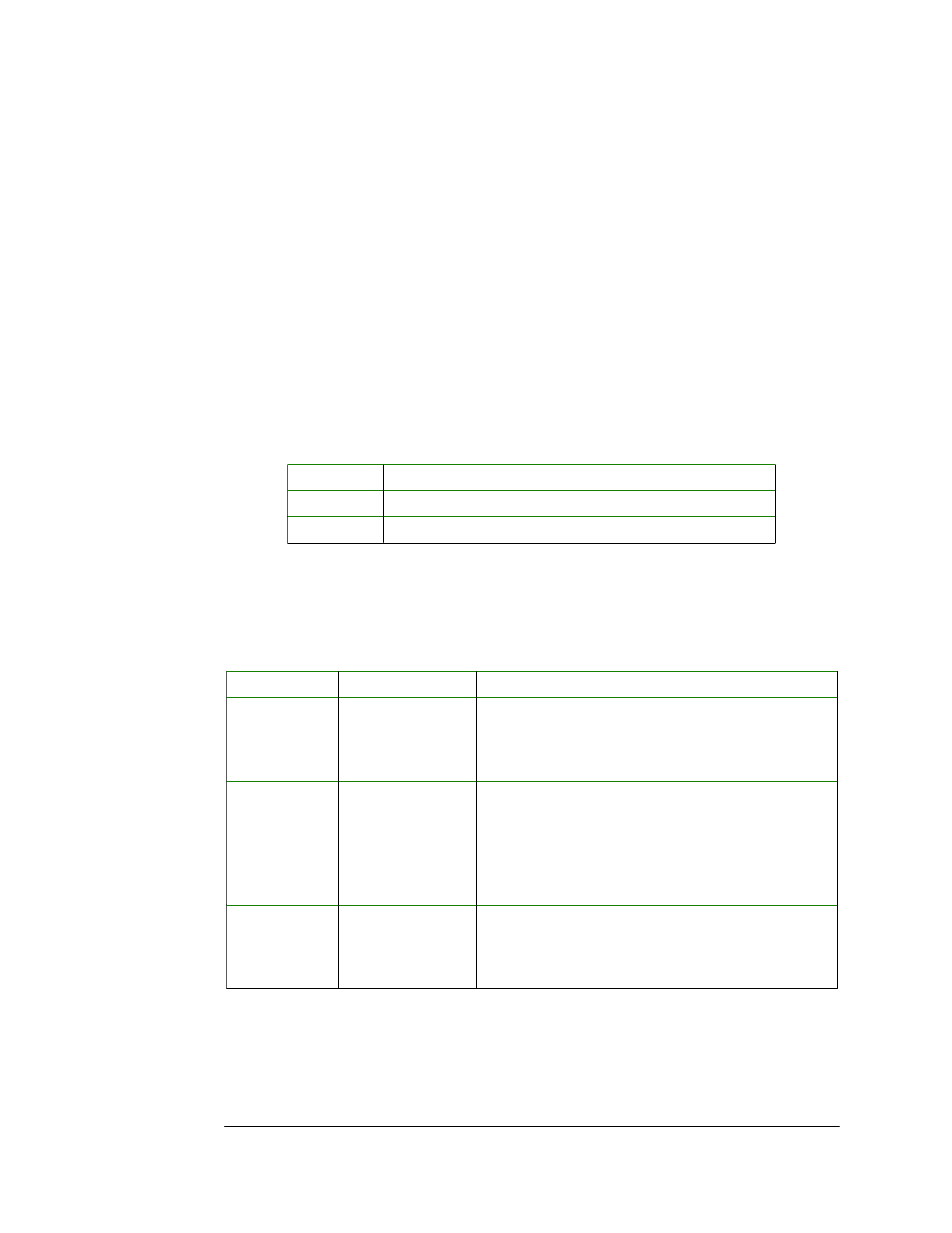

These bits are not used.

4:0

Sets the mode of the EPP port. (see the table below)

7:5

Description

Bit

Figure 19. Extended Control Register Table

Three parallel port modes are available, as described below:

In this mode, EPP cycles are initiated by writing

and reading the EPP Address Register and the

EPP Data Registers. In this mode, the control lines

have active pull-ups.

EPP Mode

'100'

This mode is identical to the Standard Parallel Port

mode except that the Direction bit may be used to

set the parallel data lines D0-D7 for input. The

value of the parallel data lines D0-D7 may be

accessed by reading the Data Register. In this

mode, the control lines have active pull-ups.

Bi-directional

Mode

'001'

In this mode, the parallel data bits D0-D7 may be

used as output only; The Direction bit has no

effect. In this mode, the control lines are driven by

open collector drivers.

Standard Parallel

Port Mode

'000'

Description

Mode

Bits[7:5]

Figure 20. Parallel Port Modes Table

NOTE:

If the EPP mode is selected, the bi-directional mode is also

available. When no EPP cycle is currently executing, the parallel port is

fully operational in the bi-directional mode.

Quatech Inc.

8-5