2 program register description, 1 data register (base + 0) – B&B Electronics SPP-100 - Manual User Manual

Page 50

8.2 Program Register description

The program register description information provided is a technical

description of the interface to parallel devices. This information is

intended for advance users intending to do custom programming with

the SPP-100.

8.2.1 Data Register (Base + 0)

The Data Register is used to write data into and read data from the

external data port (D0-D7). A write to the Data Register latches a byte of

data into this register. In the standard (unidirectional) mode, the contents

of the Data Register are always buffered and output onto the external data

port (D1-D8). In the bi-directional or EPP mode, the contents of the Data

Register are only output onto the external data port if Direction (bit 5 of

the Device Control Register) is set low; if Direction is set high, the external

data port may be accessed by reading the Data Register. In the standard

mode (or bi-directional or EPP mode with Direction set low) reading the

Data Register will access the last byte written to the Data Register.

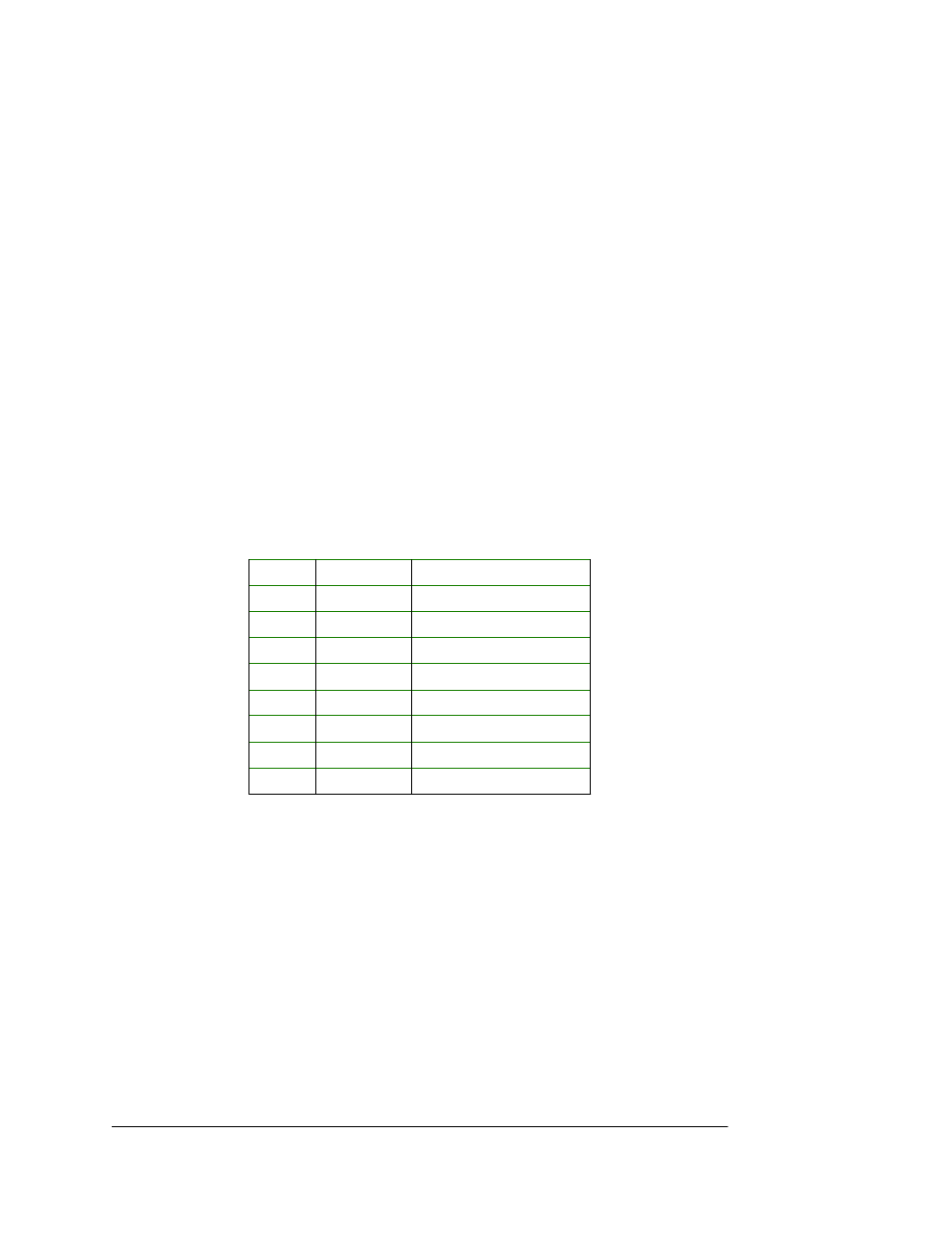

Parallel Port Data 1

D1

0

Parallel Port Data 2

D2

1

Parallel Port Data 3

D3

2

Parallel Port Data 4

D4

3

Parallel Port Data 5

D5

4

Parallel Port Data 6

D6

5

Parallel Port Data 7

D7

6

Parallel Port Data 8

D8

7

Description

Name

Bit

Figure 16. Data Register Table

8-2

Quatech Inc.