Electrical characteristics (continued) – Rainbow Electronics MAX3942 User Manual

Page 3

MAX3942

10Gbps Modulator Driver

_______________________________________________________________________________________

3

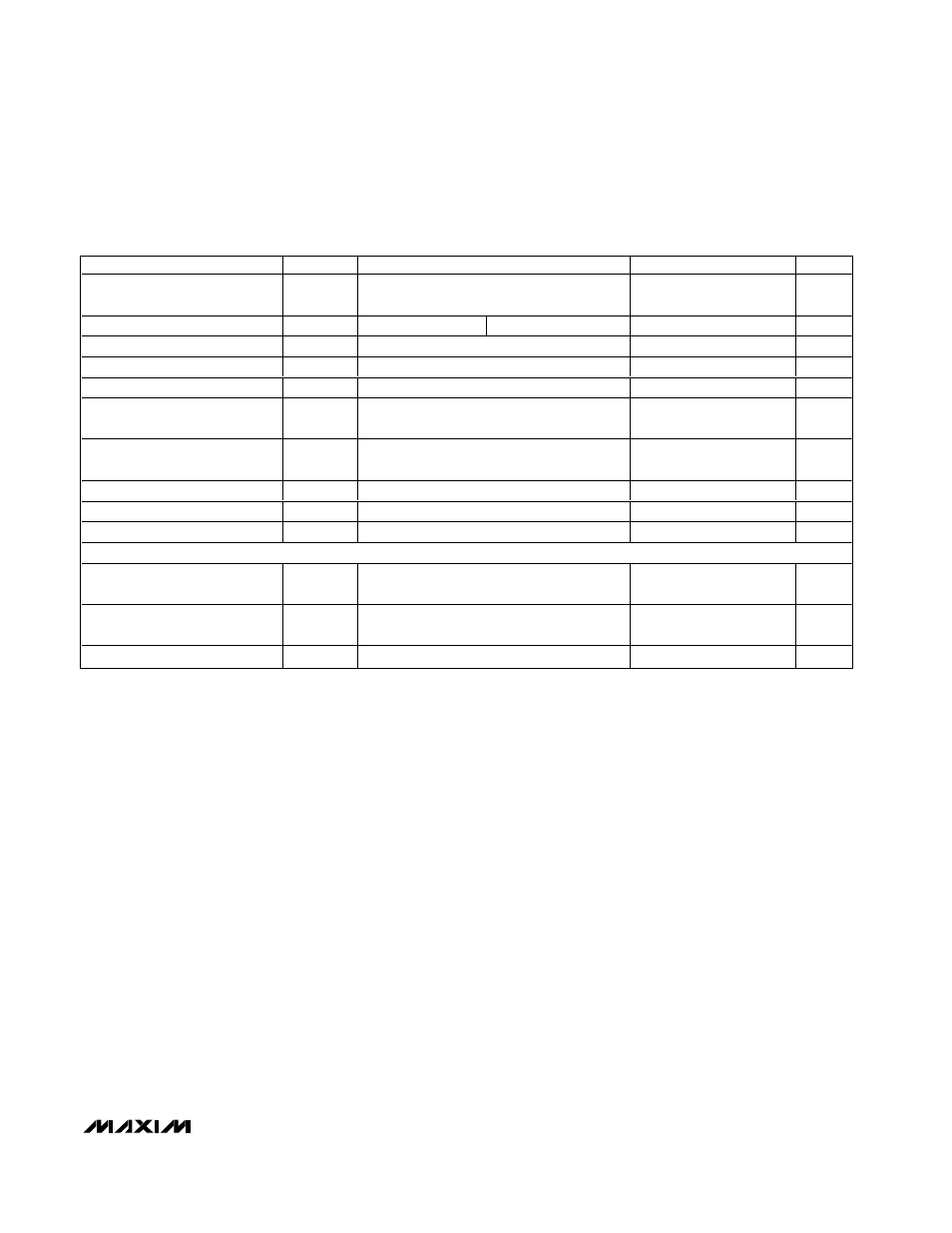

ELECTRICAL CHARACTERISTICS (continued)

(V

EE

= -5.5V to -4.9V, T

A

= -40°C to +85°C. Typical values are at V

EE

= -5.2V, I

MOD

= 100mA, and T

A

= +25°C, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Off Current

MODEN = V

EE

, MODSET = V

EE

, DATA+ =

high, DATA- = low

1.6

mA

Differential Output Return Loss

RL

OUT

I

MOD

= 50mA

≤ 10GHz

10

dB

Output Edge Speed

20% to 80% (Notes 6, 8)

23

32

ps

Setup/Hold Time

t

SU

, t

HD

Figure 2 (Note 6)

25

ps

Pulse-Width Adjustment Range

(Notes 6, 8)

±30

±50

ps

Pulse-Width Control Input Range

(Single Ended)

For PWC+ and PWC-

V

EE

+

0.5

V

EE

+

1.5

V

Pulse-Width Control Input Range

(Differential)

(PWC+) - (PWC-)

-0.5

+0.5

V

Output Overshoot

δ

(Notes 6, 8)

5

%

Driver Random Jitter

RJ

DR

(Note 6)

0.3

0.8

ps

RMS

Driver Deterministic Jitter

DJ

DR

PWC- = GND (Notes 6, 9)

8

13

ps

P-P

CONTROL INPUTS

Input High Voltage

V

IH

(Note 10)

V

EE

+

2.0

V

Input Low Voltage

V

IL

(Note 10)

V

EE

+

0.8

V

Input Current

(Note 10)

-80

+200

µA

Note 1: Supply current remains elevated once the retiming function has been enabled. Power must be cycled to reduce supply

current after the retiming function has been disabled.

Note 2: Power-supply noise rejection is specified as PSNR = 20Log(V

noise (on Vcc)

/

∆V

OUT

). V

OUT

is the voltage across a 50

Ω load.

V

noise (on Vcc)

= 100mV

P-P

.

Note 3: For DATA+, DATA-, CLK+, and CLK-.

Note 4: CLK input characterized at 10.7Gbps.

Note 5: Minimum voltage on OUT+ and OUT- is V

EE

+ 1.9V.

Note 6: Guaranteed by design and characterization using the circuit shown in Figure 3.

Note 7: R

MODEQV

= (V

MODSET

- V

EE

) / (I

MOD

- 37mA).

Note 8: 50

Ω load, characterized at 10.7Gbps with a 1111 1111 0000 0000 pattern.

Note 9: Deterministic jitter is defined as the arithmetic sum of PWD (pulse-width distortion) and PDJ (pattern-dependent jitter).

Measured with a 10.7Gbps 2

7

- 1 PRBS pattern with 80 zeros and 80 ones inserted in the data pattern.

Note 10: For MODEN and PLRT.