Description, Block diagrams, Figure 1-1 liu external connections – Rainbow Electronics DS3184 User Manual

Page 3: 1 block diagrams

Maxim/Dallas Semiconductor Confidential

Product Preview:

DS3181,2,3,4

Rev 1.5

3 of 13

022304

DESCRIPTION

The DS3184 (quad), DS3183 (triple), DS3182 (dual), and DS3181 (single) PHYs perform all of the

functions necessary for mapping/demapping ATM cells and/or packets into as many as four DS3/E3 data

streams on T3 or E3 physical copper lines. Each line interface unit (LIU) has independent receive and

transmit paths. The Receive LIU block performs clock and data recovery from a B3ZS- or HDB3-coded

AMI signal and monitors for loss of the incoming signal. The Receive Framer block optionally performs

B3ZS/HDB3 decoding. The Transmit Formatter optionally performs B3ZS/HDB3 encoding, and drives

standard pulse-shape waveforms onto 75-ohm coaxial cable. Dedicated cell processor and packet

processor blocks prepare outgoing cells or packets for transmission and check incoming cells or packets

upon arrival. Built-in DS3/E3 framers transmit and receive cell/packet data in properly formatted M23

DS3, C-bit DS3, G.751 E3 or G.832 E3 data streams. PLCP framers provide legacy ATM transmission-

convergence support. With integrated hardware support for both cells and packets, the DS3184/3/2/1

PHYs enable high-density universal line cards for unchannelized DS3/E3 from T3/E3 copper lines to

ATM/Packet system switch interface. The DS318x ATM/Packet PHYs with embedded LIU conform to

the telecommunications standards listed in section 4.

1 BLOCK

DIAGRAMS

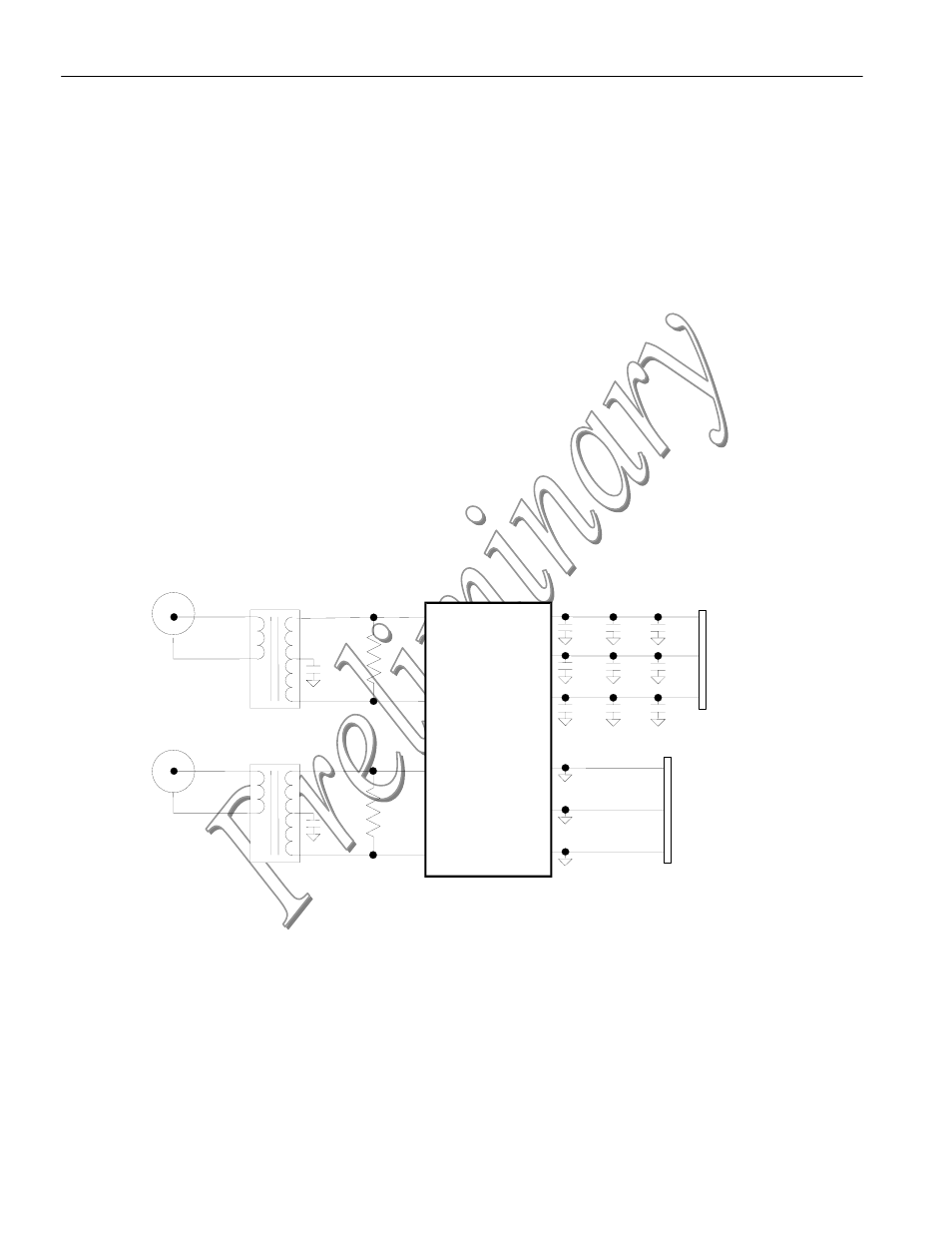

Figure 1-1 shows the external components required at each LIU interface for proper operation. Figure 1-2

shows the functional block diagram of one channel ATM / Packet PHY.

Figure 1-1 LIU External Connections

Each T3/E3 LIU Interface

Transmit

TXP

1:2ct

1:2ct

0.05uF

Receive

TXN

RXP

RXN

VDD

1uF

0.01uF

0.1uF

3.3V

Power

330

Ω

VDD

1uF

(1%)

0.1uF

0.01uF

Plane

VDD

1uF

0.1uF

0.01uF

VSS

Ground

330

Ω

VSS

0.05uF

(1%)

Plane

VSS