Serial downloading, Attiny2313 – Rainbow Electronics ATtiny2313 User Manual

Page 173

173

ATtiny2313

2543A–AVR–08/03

Notes:

1. t

WLRH

is valid for the Write Flash, Write EEPROM, Write Fuse bits and Write Lock

bits commands.

2. t

WLRH_CE

is valid for the Chip Erase command.

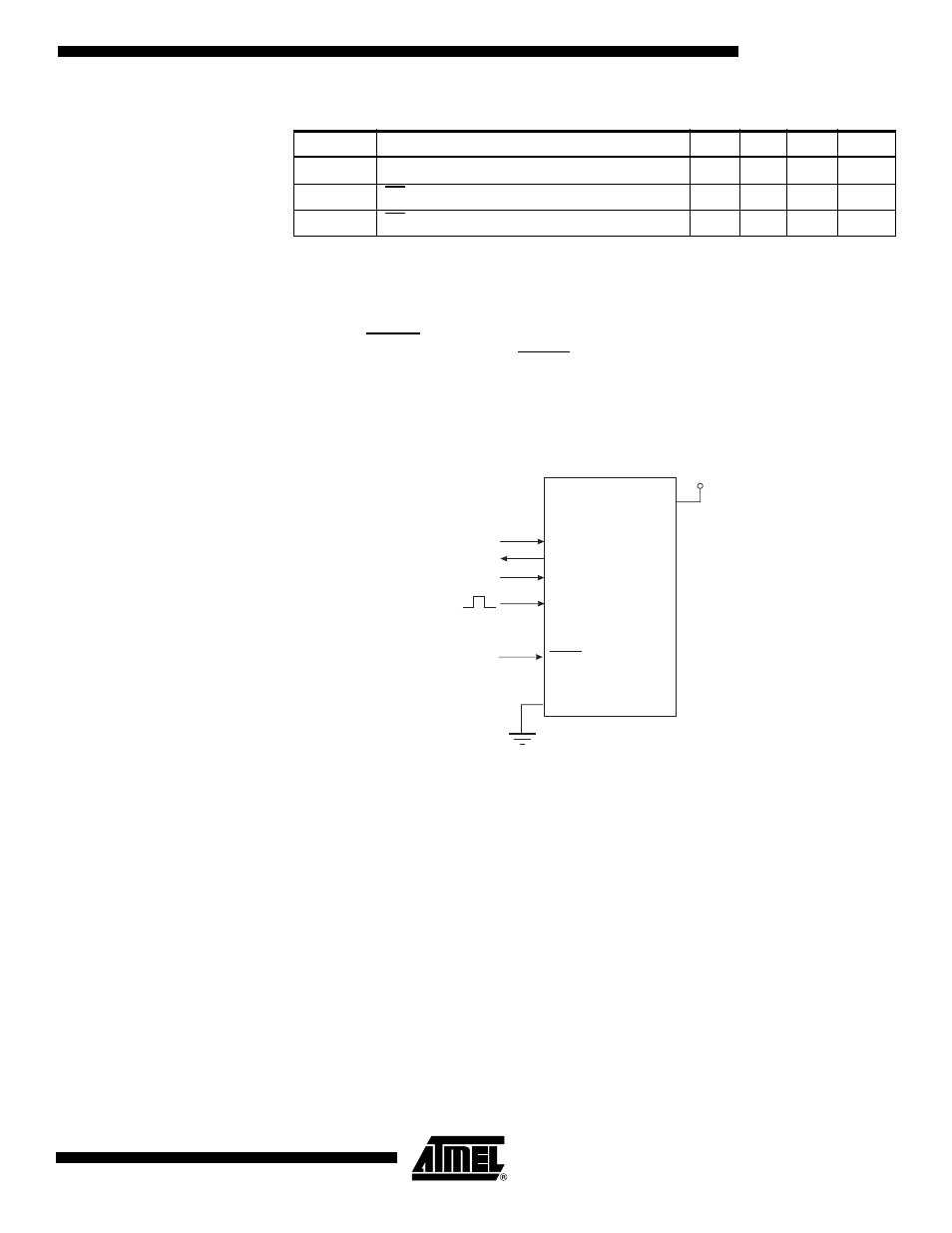

Serial Downloading

Both the Flash and EEPROM memory arrays can be programmed using the serial SPI

bus while RESET is pulled to GND. The serial interface consists of pins SCK, MOSI

(input) and MISO (output). After RESET is set low, the Programming Enable instruction

needs to be executed first before program/erase operations can be executed. NOTE, in

Table 76 on page 165, the pin mapping for SPI programming is listed. Not all parts use

the SPI pins dedicated for the internal SPI interface.

Figure 77. Serial Programming and Verify

(1)

Notes:

1. If the device is clocked by the internal Oscillator, it is no need to connect a clock

source to the XTAL1 pin.

2. V

CC

- 0.3V < AVCC < V

CC

+ 0.3V, however, AVCC should always be within 1.8 - 5.5V

When programming the EEPROM, an auto-erase cycle is built into the self-timed pro-

gramming operation (in the Serial mode ONLY) and there is no need to first execute the

Chip Erase instruction. The Chip Erase operation turns the content of every memory

location in both the Program and EEPROM arrays into 0xFF.

Depending on CKSEL Fuses, a valid clock must be present. The minimum low and high

periods for the serial clock (SCK) input are defined as follows:

Low:> 2 CPU clock cycles for f

ck

< 12 MHz, 3 CPU clock cycles for f

ck

>= 12 MHz

High:> 2 CPU clock cycles for f

ck

< 12 MHz, 3 CPU clock cycles for f

ck

>= 12 MHz

t

BVDV

BS1 Valid to DATA valid

0

250

ns

t

OLDV

OE Low to DATA Valid

250

ns

t

OHDZ

OE High to DATA Tri-stated

250

ns

Table 77. Parallel Programming Characteristics, V

CC

= 5V ± 10% (Continued)

Symbol

Parameter

Min

Typ

Max

Units

VCC

GND

XTAL1

SCK

MISO

MOSI

RESET

+1.8 - 5.5V