Functional descriptions, Three-wire mode, Attiny2313 – Rainbow Electronics ATtiny2313 User Manual

Page 141

141

ATtiny2313

2543A–AVR–08/03

The Two-wire clock control unit can generate an interrupt when a start condition is

detected on the Two-wire bus. It can also generate wait states by holding the clock pin

low after a start condition is detected, or after the counter overflows.

Functional Descriptions

Three-wire Mode

The USI Three-wire mode is compliant to the Serial Peripheral Interface (SPI) mode 0

and 1, but does not have the slave select (SS) pin functionality. However, this feature

can be implemented in software if necessary. Pin names used by this mode are: DI, DO,

and USCK.

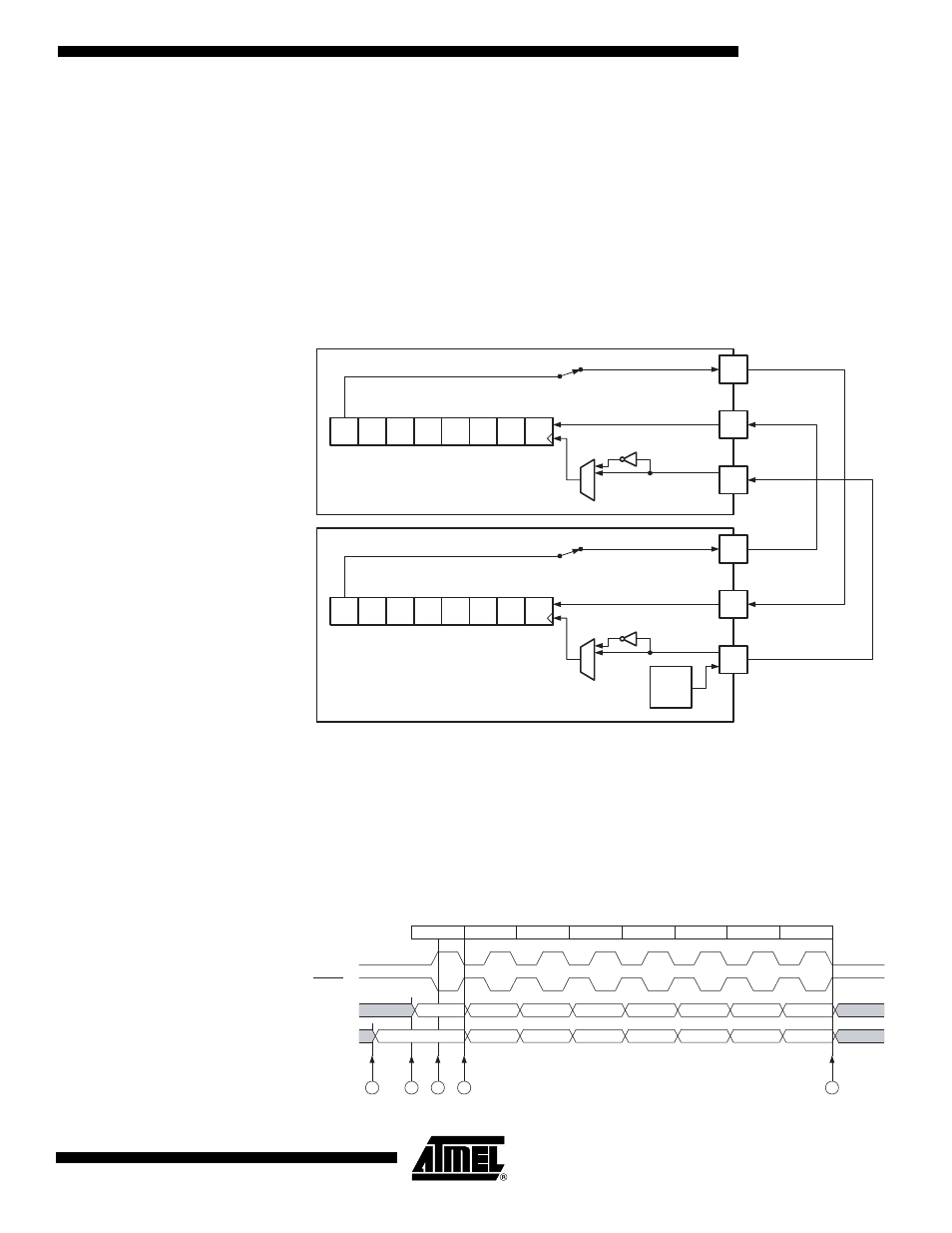

Figure 60. Three-wire Mode Operation, Simplified Diagram

Figure 60 shows two USI units operating in Three-wire mode, one as Master and one as

Slave. The two Shift Registers are interconnected in such way that after eight USCK

clocks, the data in each register are interchanged. The same clock also increments the

USI’s 4-bit counter. The Counter Overflow (interrupt) Flag, or USIOIF, can therefore be

used to determine when a transfer is completed. The clock is generated by the Master

device software by toggling the USCK pin via the PORT Register or by writing a one to

the USITC bit in USICR.

Figure 61. Three-wire Mode, Timing Diagram

SLAVE

MASTER

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

DO

DI

USCK

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

DO

DI

USCK

PORTxn

MSB

MSB

6

5

4

3

2

1

LSB

1

2

3

4

5

6

7

8

6

5

4

3

2

1

LSB

USCK

USCK

DO

DI

D

C

B

A

E

CYCLE

( Reference )