Instruction execution timing, Reset and interrupt handling, Attiny2313 – Rainbow Electronics ATtiny2313 User Manual

Page 10

10

ATtiny2313

2543A–AVR–08/03

Instruction Execution

Timing

This section describes the general access timing concepts for instruction execution. The

AVR CPU is driven by the CPU clock clk

CPU

, directly generated from the selected clock

source for the chip. No internal clock division is used.

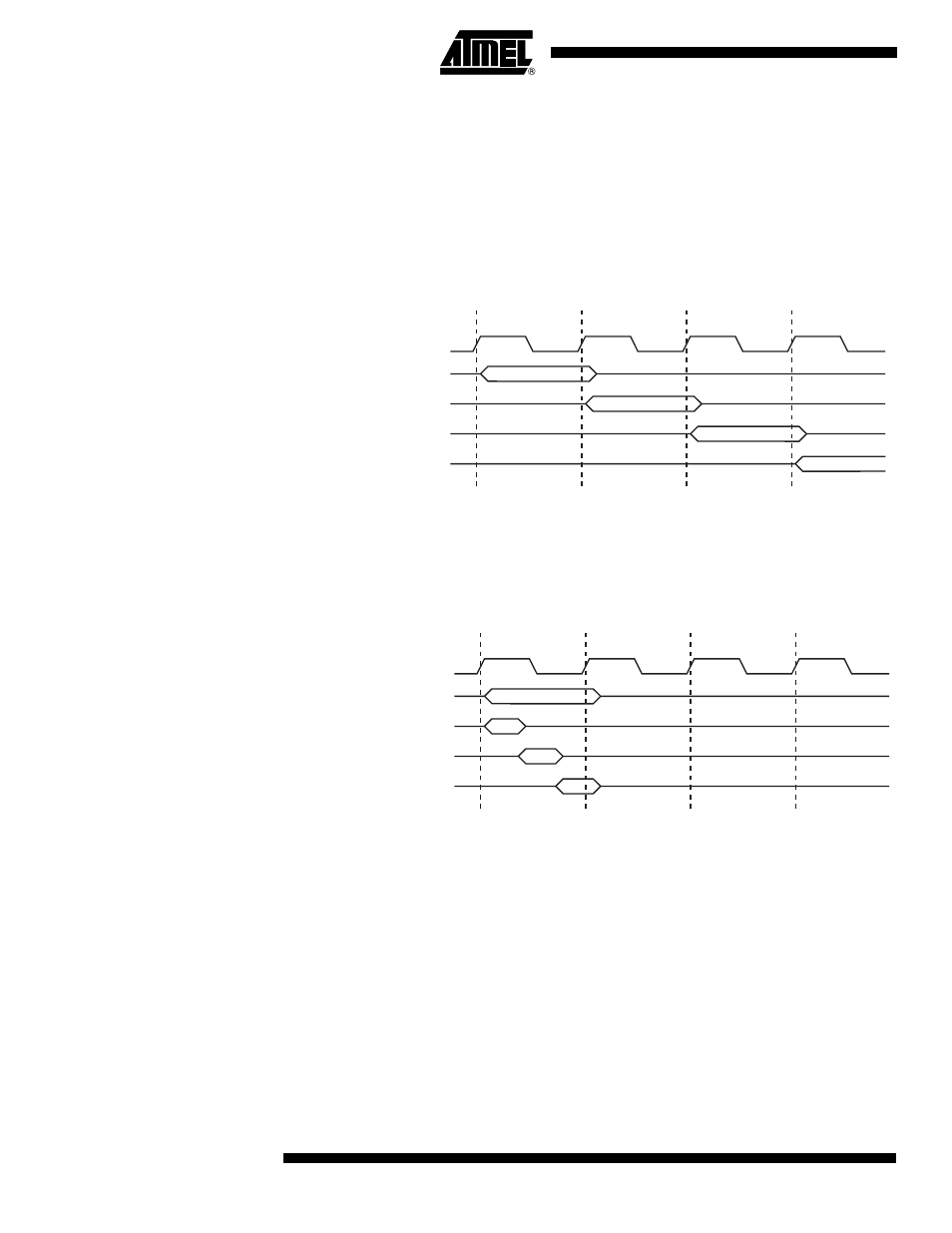

Figure 6 shows the parallel instruction fetches and instruction executions enabled by the

Harvard architecture and the fast-access Register File concept. This is the basic pipelin-

ing concept to obtain up to 1 MIPS per MHz with the corresponding unique results for

functions per cost, functions per clocks, and functions per power-unit.

Figure 6. The Parallel Instruction Fetches and Instruction Executions

Figure 7 shows the internal timing concept for the Register File. In a single clock cycle

an ALU operation using two register operands is executed, and the result is stored back

to the destination register.

Figure 7. Single Cycle ALU Operation

Reset and Interrupt

Handling

The AVR provides several different interrupt sources. These interrupts and the separate

Reset Vector each have a separate program vector in the program memory space. All

interrupts are assigned individual enable bits which must be written logic one together

with the Global Interrupt Enable bit in the Status Register in order to enable the interrupt.

The lowest addresses in the program memory space are by default defined as the Reset

and Interrupt Vectors. The complete list of vectors is shown in “Interrupts” on page 45.

The list also determines the priority levels of the different interrupts. The lower the

address the higher is the priority level. RESET has the highest priority, and next is INT0

– the External Interrupt Request 0. Refer to “Interrupts” on page 45 for more information.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared and all interrupts

are disabled. The user software can write logic one to the I-bit to enable nested inter-

rupts. All enabled interrupts can then interrupt the current interrupt routine. The I-bit is

automatically set when a Return from Interrupt instruction – RETI – is executed.

clk

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

T1

T2

T3

T4

CPU

Total Execution Time

Register Operands Fetch

ALU Operation Execute

Result Write Back

T1

T2

T3

T4

clk

CPU