Ra01 – Rainbow Electronics RA01 User Manual

Page 17

RA01

Version: 1.0 Date: 10/8/2008

Dual Clock Output

When the chip is switched into idle mode, the 10 MHz crystal oscillator starts. After oscillation ramp-up a 1 MHz

clock signal is available on the CLK pin. This (fast) clock frequency can be reprogrammed during operation with the

Low Battery and Microcontroller Clock Divider Command

(page12). During startup and in sleep or standby mode

(crystal oscillator disabled), the CLK output is pulled to logic low.

On the same pin a low frequency clock signal can be obtained if the

elfc

bit is set in the

Low Battery and

Microcontroller Clock Divider Command

. The clock frequency is 32 kHz which is derived from the low-power RC

oscillator of the wake-up timer. In order to use this slow clock the wake-up timer should be enabled by setting the

et

bit in the

Configuration Setting Command

(page 9) even if the wake-up timer itself is not used.

Slow clock feature can be enabled by entering into sleep mode (page 17). Driving the output will increase the sleep

mode supply current. Actual worst-case value can be determined when the exact load and min/max operating

conditions are defined. After power-on reset the chip goes into sleep mode and the slow frequency clock appears

on the CLK pin.

Switching back into fast clock mode can be done by setting the

ex

or

en

bits in the appropriate commands. It is

important to leave bit

dc

in the

Configuration Setting Command

at its default state (0) otherwise there will be no

clock signal on the CLK pin.

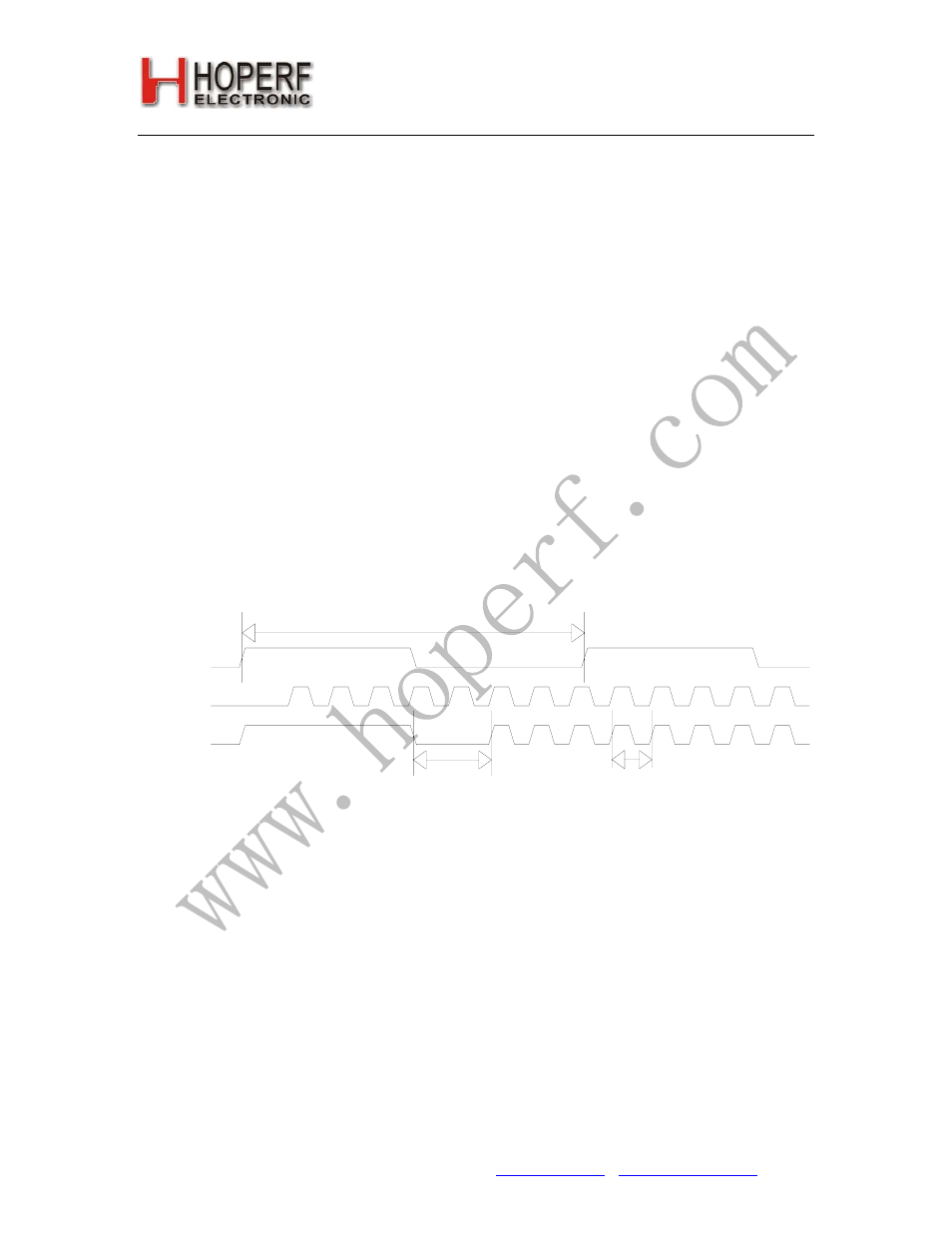

Switching between the fast and slow clock modes is glitch-free in a sense that either state of the clock lasts for at

least a half cycle of the fast clock. During switching the clock can be logic low once for an intermediate period i.e. for

any time between the half cycle of the fast and the slow clock.

Tel: +86-755-82973805 Fax: +86-755-82973550 E-mail: [email protected] http://www.hoperf.com

17

0.5*Tfast

output

fast clock

slow clock

Tslow

Tfast

Tx

Clock period are not to scale

The clock switching synchronization circuit detects the falling edges of the clocks. One consequence is a latency of

0 to T

slow

+ T

fast

from the occurrence of a clock change request (entering into sleep mode or interrupt) until the

beginning of the intermediate length (T

x

) half cycle. The other is that both clocks should be up and running for the

change to occur. Changing from fast to slow clock, it is automatically ensured by entering into the sleep mode in the

appropriate way provided that the wake-up timer is continuously enabled. As the crystal oscillator is normally

stopped while the slow clock is used, when changing back to fast clock the crystal oscillator startup time has to pass

first before the above mentioned latency period starts. The startup condition is detected internally, so no software

timing is necessary.