Ra01, Status read command, Status register read sequence – Rainbow Electronics RA01 User Manual

Page 15: Polling mode, Fifo buffered data read

RA01

Version: 1.0 Date: 10/8/2008

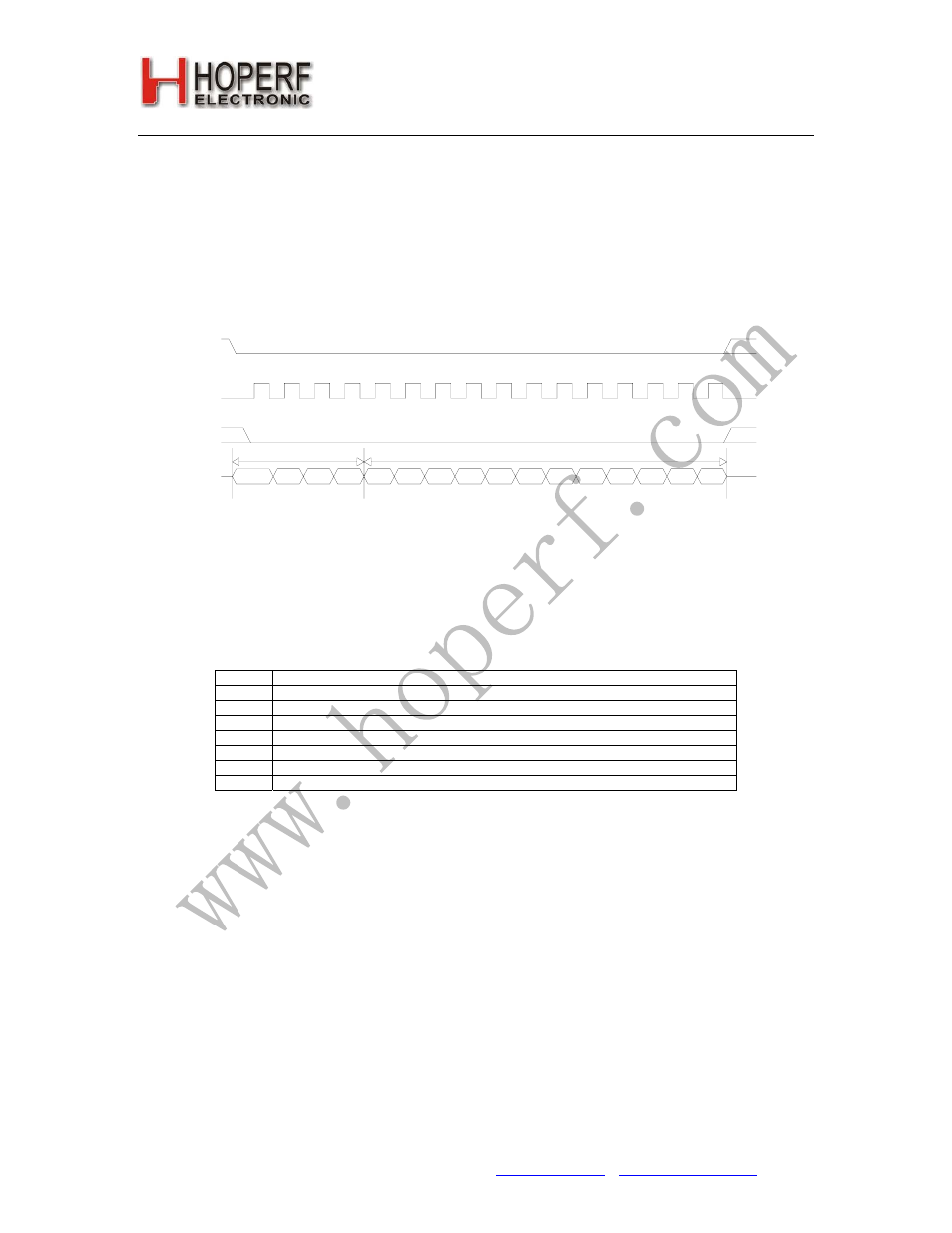

13. Status Read Command

The read command starts with a zero, whereas all other control commands start with a one. Therefore, after

receiving the first bit of the control command the RA01 identifies it as a read command. So as the first bit of the

command is received, the receiver starts to clock out the status bits on the SDO output as follows:

Status Register Read Sequence

Tel: +86-755-82973805 Fax: +86-755-82973550 E-mail: [email protected] http://www.hoperf.com

15

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

FIFO IT FFOV*WK-UP* LBD* FFEM RSSIH RSSIM RSSIL

0

0

0

0

0

0

0

0

nSEL

SCK

SDI

SDO

Interrupt bits out

status bits out

NOTE: *Bits marked are internally latched.

Others are only mutiplexed

Definitions of the bits in the above timing diagram:

FFIT

The number of data bits in the FIFO has reached the preprogrammed limit

FFOV

FIFO overflow

WK-UP

Wake-up timer overflow

LBD

Low battery detect, the power supply voltage is below the preprogrammed limit

FFEM

FIFO is empty

RSSIH

Input signal above tbd. dBm

RSSIM

Input signal above tbd. dBm

RSSIL

Input signal above tbd. dBm

FIFO Buffered Data Read

In this operating mode, incoming data are clocked into a 64 bit FIFO buffer. The receiver starts to fill up the FIFO

when the Valid Data Indicator (VDI) bit and/or the synchron word recognition circuit indicates potentially real

incoming data. This prevents the FIFO from being filled with noise and overloading the external microcontroller.

For further details see the Receiver Setting Command and the Output and FIFO Command.

Polling Mode:

The nFFS signal selects the buffer directly and its content could be clocked out through pin SDO by SCK. Set the

FIFO IT level to 1. In this case, as long as FFIT indicates received bits in the FIFO, the controller may continue to

take the bits away. When FFIT goes low, no more bits need to be taken. An SPI read command is also available.