Functional diagram, Pin description (continued), Detailed description – Rainbow Electronics MAX7033 User Manual

Page 9

MAX7033

315MHz/433MHz ASK Superheterodyne

Receiver with AGC Lock

_______________________________________________________________________________________

9

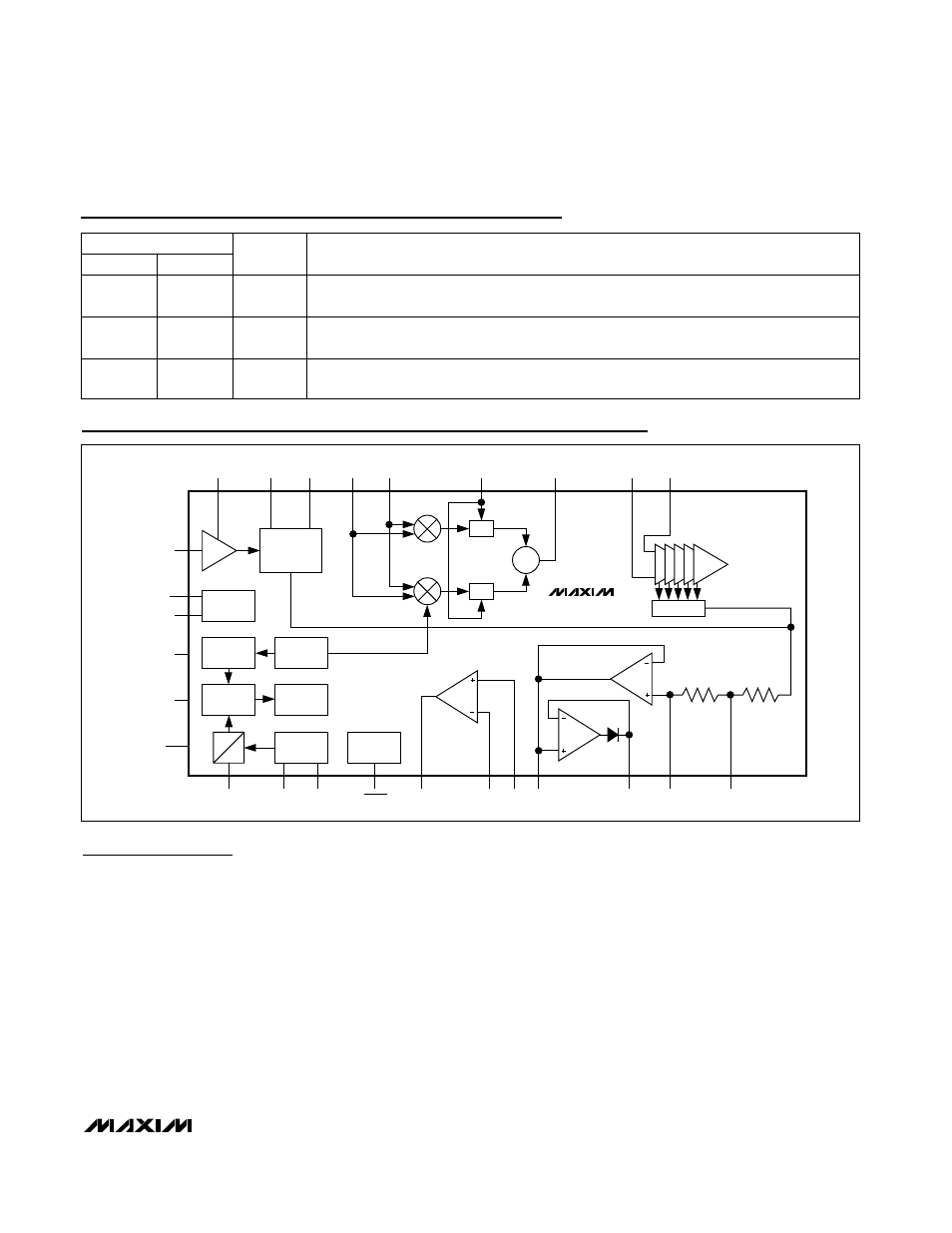

Functional Diagram

LNAOUT

MIXIN1 MIXIN2

0˚

90˚

IFIN1

MIXOUT

IFIN2

RSSI

R

DF2

100k

Ω

R

DF1

100k

Ω

DIVIDE

BY 64

VCO

LOOP

FILTER

PHASE

DETECTOR

CRYSTAL

DRIVER

POWER-

DOWN

IF LIMITING

AMPS

14

LNASRC

DATA

SLICER

DATA

FILTER

Q

∑

I

AUTOMATIC

GAIN

CONTROL

IMAGE

REJECTION

3.2V REG

24

2, 7

IRSEL

13

5, 10

AV

DD

V

DD5

DV

DD

DGND

AGND

LNAIN

3

XTALSEL

16

XTAL1

1

XTAL2

28

SHDN

27

DATAOUT

25

DSN

20

DSP

23

DFO

19

PDOUT

26

OPP

21

DFFB

22

4

15

6

8

9

11

12

17

18

AC

ч2

ч1

MAX7033

LNA

28-PIN TSSOP

PACKAGE

Pin Description (continued)

PIN

TSSOP

THIN QFN

NAME

FUNCTION

27

27

SHDN

Power-Down Select Input. Drive high to power up the IC. Internally pulled down to AGND

with a 100k

Ω resistor.

28

28

XTAL2

Crystal Input 2. Can also be driven with an external reference oscillator. (See the Crystal

Oscillator section.)

—

1, 13, 21,

25

N.C

No Connection

Detailed Description

The MAX7033 CMOS superheterodyne receiver and a

few external components provide the complete receive

chain from the antenna to the digital output data.

Depending on signal power and component selection,

data rates as high as 33kbps Manchester (66kbps

NRZ) can be achieved.

The MAX7033 is designed to receive binary ASK data

modulated in the 300MHz to 450MHz frequency range.

ASK modulation uses a difference in amplitude of the

carrier to represent logic 0 and logic 1 data.

For operation with a single +3.0V to +3.6V supply voltage,

connect AV

DD

, DV

DD

, and V

DD5

to the supply voltage.

For operation with a single +4.5V to +5.5V supply volt-

age, connect V

DD5

to the supply voltage. An on-chip

voltage regulator drives one of the AV

DD

pins to

approximately +3.2V. For proper operation, DV

DD

and

both AV

DD

pins must be connected together. Bypass

DV

DD

and both AV

DD

pins to AGND with 0.01µF

capacitors placed as close to the pins as possible.

Low-Noise Amplifier

The LNA is an nMOS cascode amplifier with off-chip

inductive degeneration, with a 3.0dB noise figure and

an IIP3 of -12dBm. The gain and noise figures are

dependent on both the antenna matching network at

the LNA input and the LC tank network between the

LNA output and the mixer inputs.