2 high speed pc interface board : b-4800-pc-qm - 2, Pc printer – Toshiba B-570 SERIES User Manual

Page 54

3-2

3. OPTIONAL KIT

EM10-33006A

3.2 HIGH SPEED PC INTERFACE BOARD: B-4800-PC-QM

Command transfer and printing can be processed quickly by connecting a PC and the printer via a FIFO

(first-in first-out) IC on the high speed PC interface board. For details, refer to the specification for high

speed PC interface.

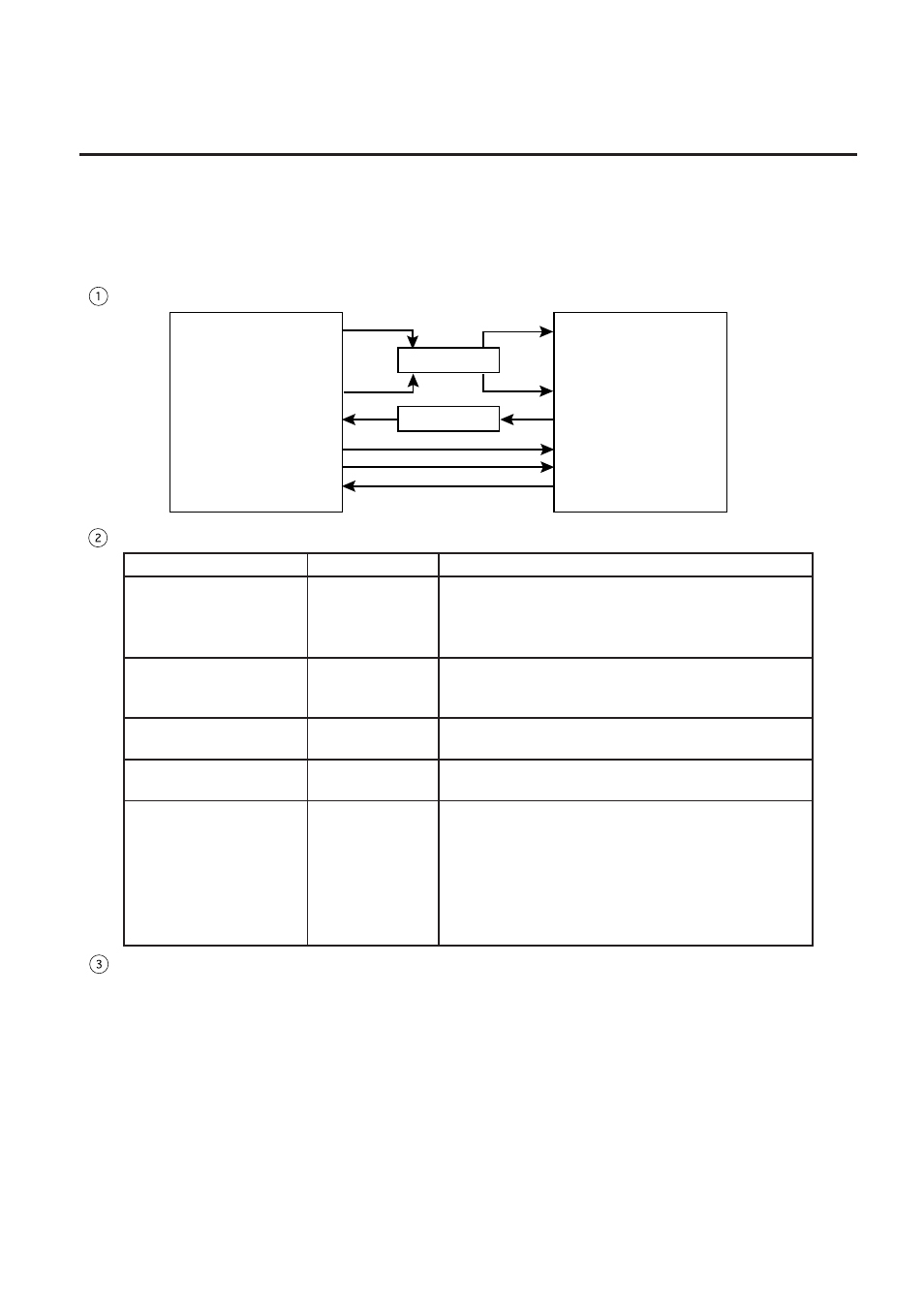

Configuration of interface

Fig. 3-2

Signal description

Transmission control

■

When a command is sent from the PC to the printer:

Confirms that the image data transfer request bit has not been ON and the FIFO is vacant, then

writes a command to the FIFO.

■

When image data is sent from the PC to the printer:

Confirms that the image data transfer request bit has been ON, then writes the image data to

the FIFO.

■

When the printer transfers image data from the PC using DMA:

Turns the image data transfer request bit high-level to start DMA. When DMA transfer of all the

image data is completed, turns the image transfer request bit low-level.

■

When a status is sent from the printer to the PC:

Writes a status to the FIFO.

3.2 HIGH SPEED PC INTERFACE BOARD : B-4800-QM

Data FIFO

Status FIFO

Command

Image data

Status

Image data

Transfer request

Command

Image data

Status request

Reset request

PC

Printer

Signal

Data FIFO

Status FIFO

Status request signal

Reset request signal

Image data transfer

request signal

Direction

PC

/

Printer

PC

,

Printer

PC

/

Printer

PC

/

Printer

PC

,

Printer

Description

FIFO to transfer commands and image data. In

case of a command, FIFO data reading is

performed by the CPU. In case of image data,

reading is performed by DMA transfer.

FIFO to transfer status. The status for a status

autosending or for status request is written by the

BPE.

The PC turns this signal high-level to request for

a status. It is cleared when reading is performed.

The PC turns this signal high-level to request for

reset. It is cleared when reading is performed.

The printer turns this signal high-level when

ready for an image data transfer. When transfer

is completed, it is turned low-level.

The PC must not write the image data to the FIFO

until this signal turns high level. Also, the PC

must confirm that this signal is low-level for

sending a command.