NEC uPD78P078 User Manual

Page 586

586

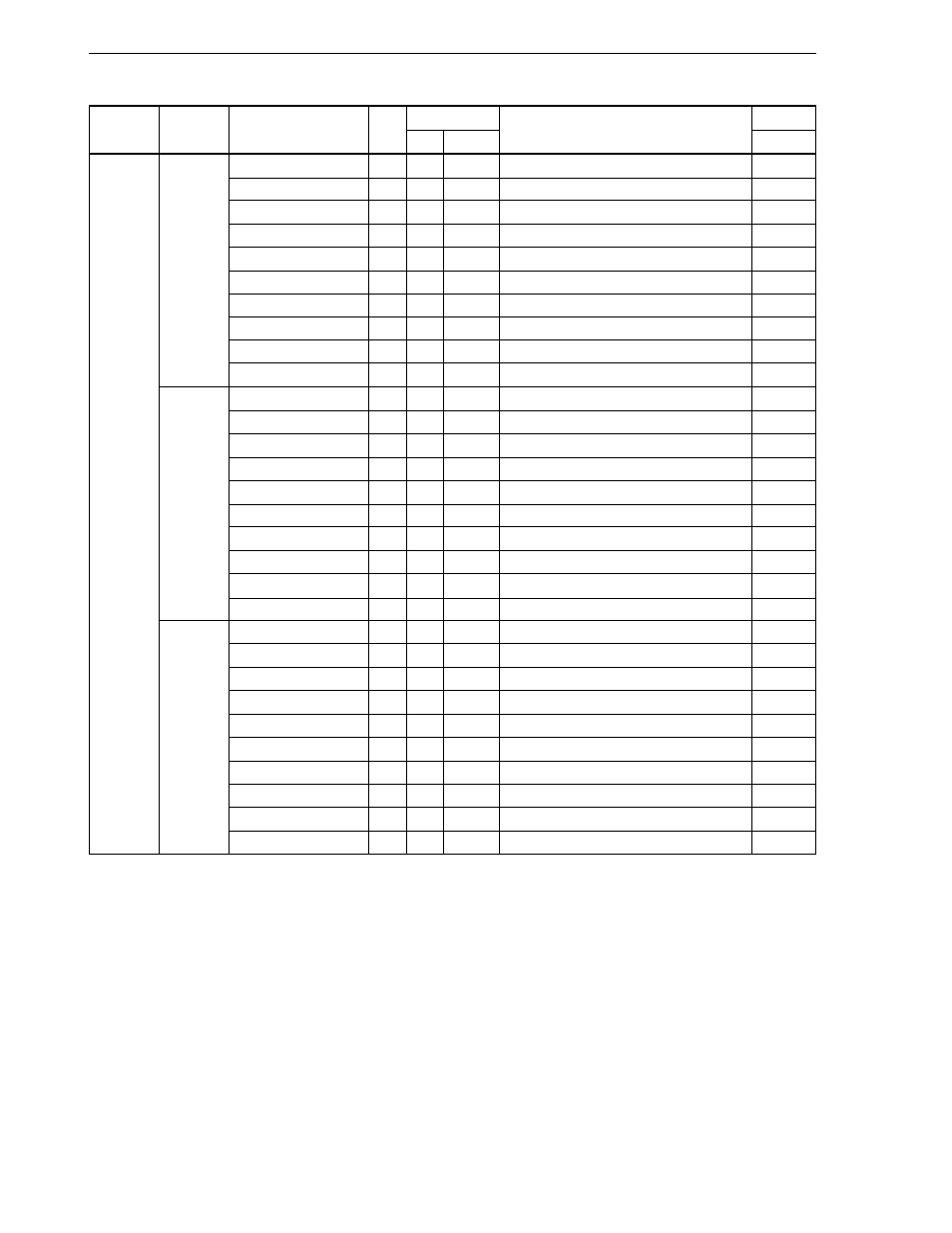

CHAPTER 28 INSTRUCTION SET

Instruction

Mnemonic

Operands

Byte

Clock

Operation

Flag

Group

Note 1

Note 2

Z AC CY

8-bit

SUB

A, #byte

2

4

—

A, CY

←

A – byte

x

x

x

operation

saddr, #byte

3

6

8

(saddr), CY

←

(saddr) – byte

x

x

x

A, r

Note 3

2

4

—

A, CY

←

A – r

x

x

x

r, A

2

4

—

r, CY

←

r – A

x

x

x

A, saddr

2

4

5

A, CY

←

A – (saddr)

x

x

x

A, !addr16

3

8

9 + n

A, CY

←

A – (addr16)

x

x

x

A, [HL]

1

4

5 + n

A, CY

←

A – (HL)

x

x

x

A, [HL + byte]

2

8

9 + n

A, CY

←

A – (HL + byte)

x

x

x

A, [HL + B]

2

8

9 + n

A, CY

←

A – (HL + B)

x

x

x

A, [HL + C]

2

8

9 + n

A, CY

←

A – (HL + C)

x

x

x

SUBC

A, #byte

2

4

—

A, CY

←

A – byte – CY

x

x

x

saddr, #byte

3

6

8

(saddr), CY

←

(saddr) – byte – CY

x

x

x

A, r

Note 3

2

4

—

A, CY

←

A – r – CY

x

x

x

r, A

2

4

—

r, CY

←

r – A – CY

x

x

x

A, saddr

2

4

5

A, CY

←

A – (saddr) – CY

x

x

x

A, !addr16

3

8

9 + n

A, CY

←

A – (addr16) – CY

x

x

x

A, [HL]

1

4

5 + n

A, CY

←

A – (HL) – CY

x

x

x

A, [HL + byte]

2

8

9 + n

A, CY

←

A – (HL + byte) – CY

x

x

x

A, [HL + B]

2

8

9 + n

A, CY

←

A – (HL + B) – CY

x

x

x

A, [HL + C]

2

8

9 + n

A, CY

←

A – (HL + C) – CY

x

x

x

AND

A, #byte

2

4

—

A

←

A /\ byte

x

saddr, #byte

3

6

8

(saddr)

←

(saddr) /\ byte

x

A, r

Note 3

2

4

—

A

←

A /\ r

x

r, A

2

4

—

r

←

r /\ A

x

A, saddr

2

4

5 + n

A

←

A /\ (saddr)

x

A, !addr16

3

8

9 + n

A

←

A /\ (addr16)

x

A, [HL]

1

4

5 + n

A

←

A /\ (HL)

x

A, [HL + byte]

2

8

9 + n

A

←

A /\ (HL + byte)

x

A, [HL + B]

2

8

9 + n

A

←

A /\ (HL + B)

x

A, [HL + C]

2

8

9 + n

A

←

A /\ (HL + C)

x

Notes 1. For instructions that access the internal high-speed RAM area or perform no data access

2. For instructions that access an area other than the internal high-speed RAM area

3. Except when “r = A”

Remarks 1. One clock in the “Clock” columns is equal to one cycle of the CPU clock (f

CPU

) selected by the processor

clock control register (PCC).

2. The values in the “Clock” column assumes that the internal ROM area contains programs.

3. n indicates wait cycles to be inserted when an external expansion memory area is read from.