NEC uPD78P078 User Manual

Page 549

549

CHAPTER 24 STANDBY FUNCTION

HALT

Instruction

RESET

Signal

Operating

Mode

Clock

Reset

Period

HALT Mode

Oscillation

Oscillation

stop

Oscillation

Stabilization

Wait Status

Operating

Mode

Oscillation

Wait

(2

17

/f

x

: 26.2 ms)

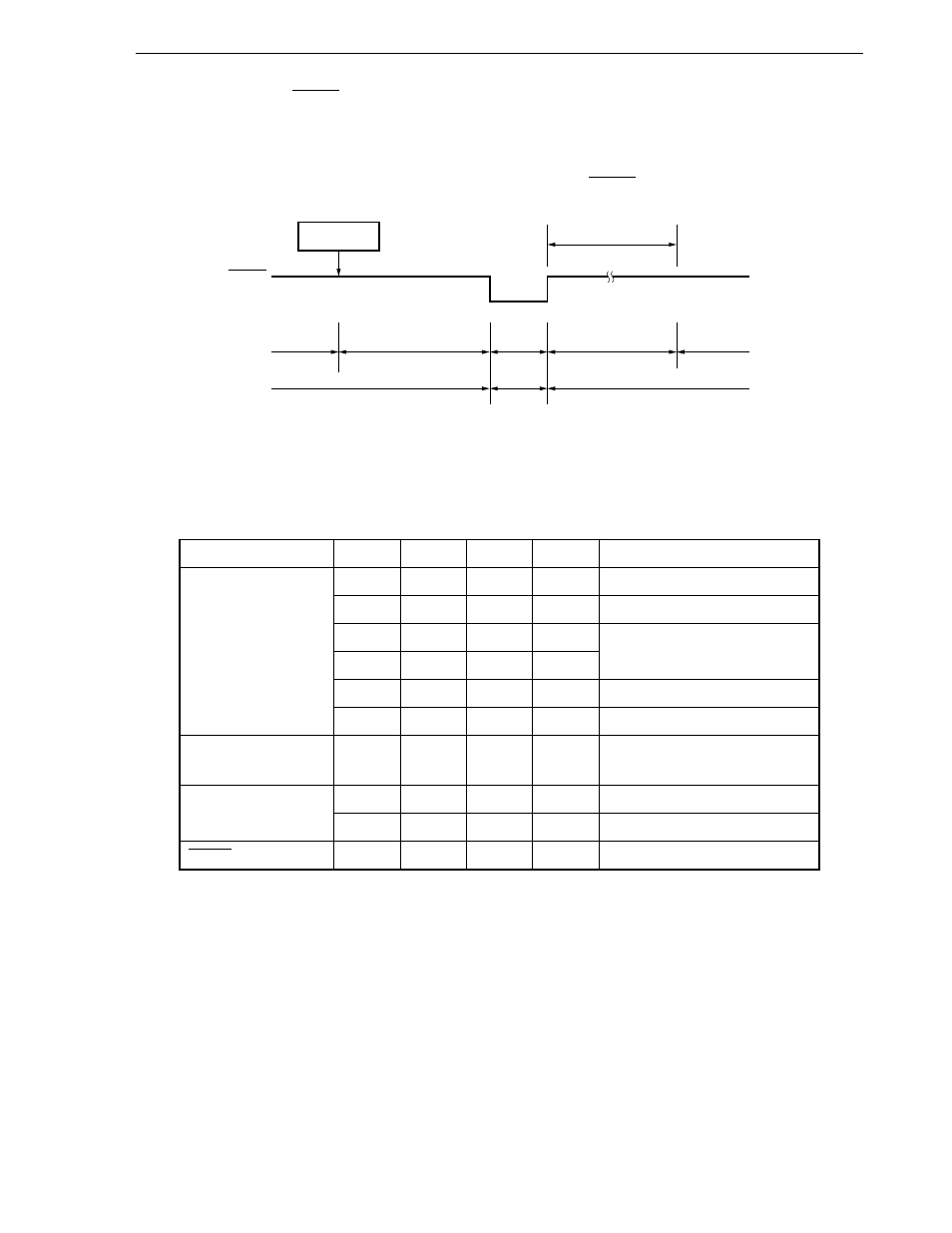

(d) Release by RESET input

As is the case with normal reset operation, a program is executed after branch to the reset vector

address.

Figure 24-3. HALT Mode Released by RESET Input

Remarks 1. f

X

: Main system clock oscillation frequency

2. Figures in parentheses apply to operation with f

X

= 5.0 MHz.

Table 24-2. Operation after HALT Mode Release

Release Source

MKxx

PRxx

IE

ISP

Operation

Maskable interrupt

0

0

0

x

Next address instruction execution

request

0

0

1

x

Interrupt service execution

0

1

0

1

Next address instruction execution

0

1

x

0

0

1

1

1

Interrupt service execution

1

x

x

x

HALT mode hold

Non-maskable interrupt

–

–

x

x

Interrupt service execution

request

Test input

0

–

x

x

Next address instruction execution

1

–

x

x

HALT mode hold

RESET input

–

–

x

x

Reset processing

x: Don’t care