2 clock generator configuration – NEC uPD78P078 User Manual

Page 166

166

CHAPTER 7 CLOCK GENERATOR

Subsystem

Clock

Oscillator

Main

System

Clock

Oscillator

X2

X1

XT2

XT1/P07

FRC

STOP

MCC

FRC

CLS CSS PCC2 PCC1

Internal Bus

Standby

Control

Circuit

To INTP0

Sampling Clock

2

f

XX

2

2

f

XX

2

3

f

XX

2

4

f

XX

Prescaler

Clock to

Peripheral

Hardware

Prescaler

Oscillation Mode

Selection Register

Watch Timer,

Clock Output

Function

f

XX

CPU Clock

(f

CPU

)

Wait

Control

Circuit

Divider

Selector

f

X

f

XT

2

f

X

MCS

Processor Clock

Control Register

1/2

2

f

XT

PCC0

3

Selector

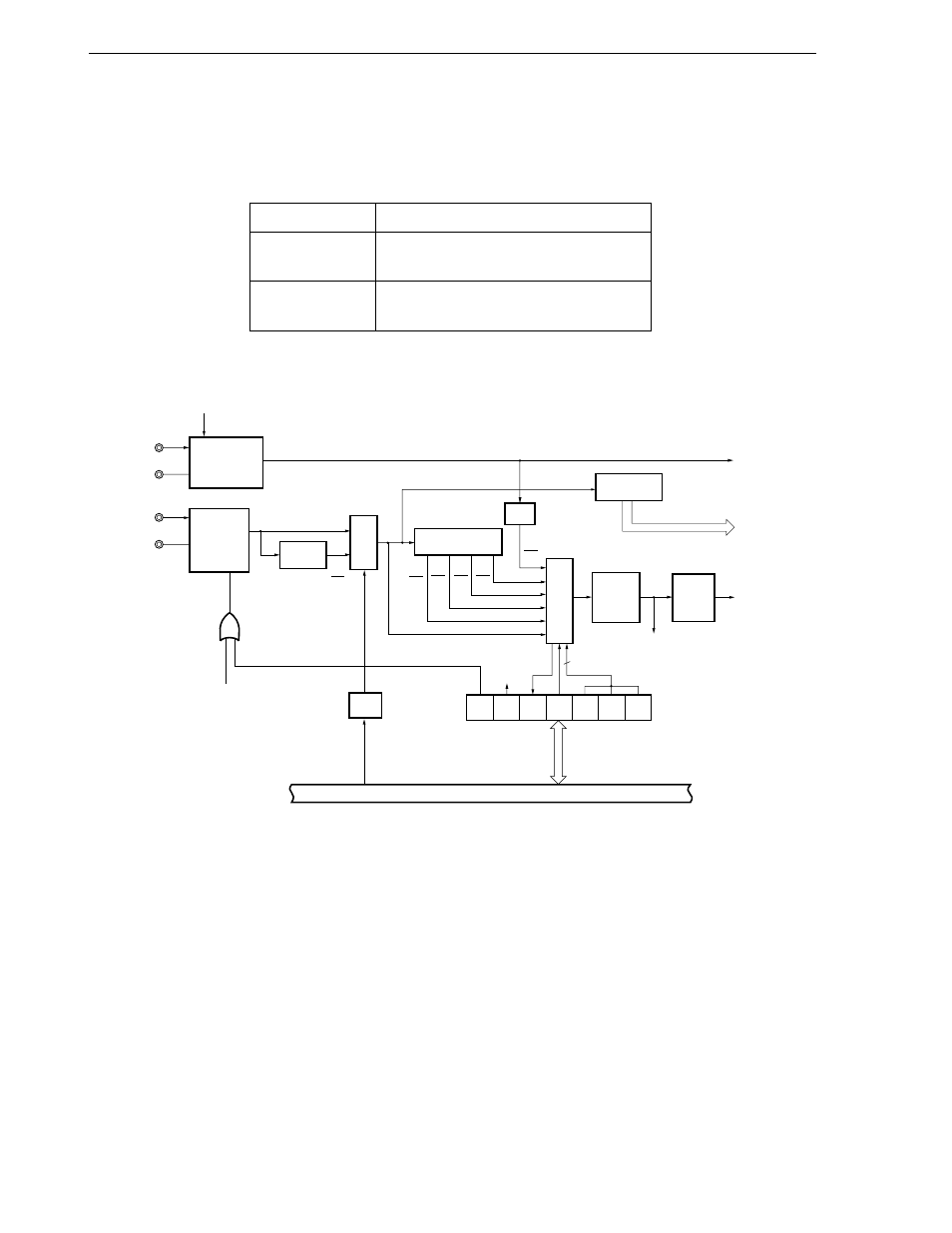

7.2 Clock Generator Configuration

The clock generator consists of the following hardware.

Table 7-1. Clock Generator Configuration

Item

Configuration

Control register

Processor clock control register (PCC)

Oscillation mode selection register (OSMS)

Oscillator

Main system clock oscillator

Subsystem clock oscillator

Figure 7-1. Block Diagram of Clock Generator