NEC uPD78P078 User Manual

Page 474

474

CHAPTER 20 SERIAL INTERFACE CHANNEL 2

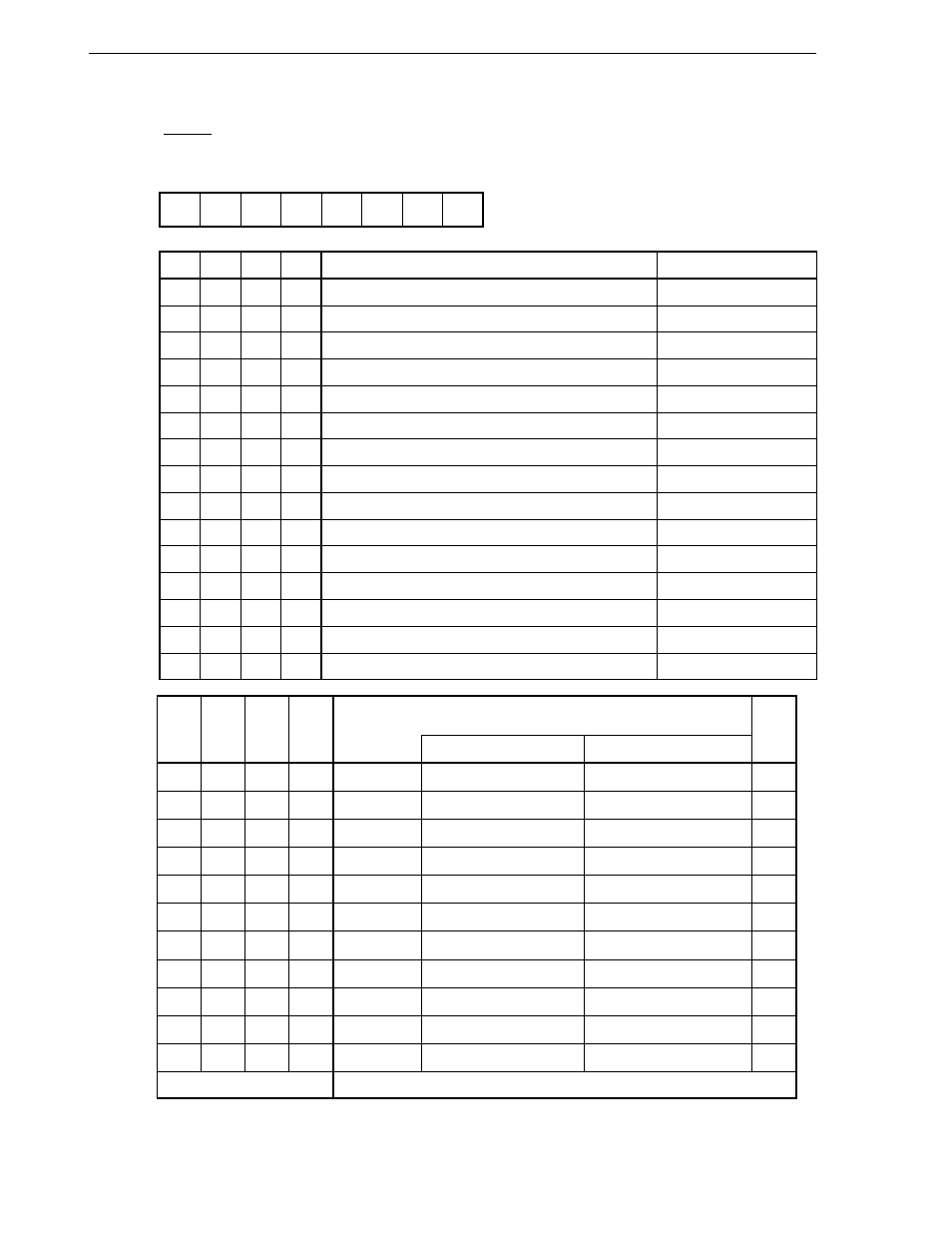

(d) Baud rate generator control register (BRGC)

BRGC is set with an 8-bit memory manipulation instruction.

RESET input sets BRGC to 00H.

Baud Rate Generator Input Clock Selection

MDL3 MDL2 MDL1 MDL0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

f

SCK

/16

f

SCK

/17

f

SCK

/18

f

SCK

/19

f

SCK

/20

f

SCK

/21

f

SCK

/22

f

SCK

/23

f

SCK

/24

f

SCK

/25

f

SCK

/26

f

SCK

/27

f

SCK

/28

f

SCK

/29

f

SCK

/30

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

6

5

4

3

2

1

0

7

Symbol

BRGC

TPS3 TPS2 TPS1 TPS0 MDL3 MDL2 MDL1 MDL0

FF73H 00H R/W

Address After Reset R/W

k

5-Bit Counter Source Clock Selection

TPS3 TPS2 TPS1 TPS0

n

MCS = 1

MCS = 0

0

0

0

0

f

XX

/2

10

f

X

/2

10

(4.9 kHz)

f

X

/2

11

(2.4 kHz)

11

0

1

0

1

f

XX

f

X

(5.0 MHz)

f

X

/2

(2.5 MHz)

1

0

1

1

0

f

XX

/2

f

X

/2

(2.5 MHz)

f

X

/2

2

(1.25 MHz)

2

0

1

1

1

f

XX

/2

2

f

X

/2

2

(1.25 MHz)

f

X

/2

3

(625 kHz)

3

1

0

0

0

f

XX

/2

3

f

X

/2

3

(625 kHz)

f

X

/2

4

(313 kHz)

4

1

0

0

1

f

XX

/2

4

f

X

/2

4

(313 kHz)

f

X

/2

5

(156 kHz)

5

1

0

1

0

f

XX

/2

5

f

X

/2

5

(156 kHz)

f

X

/2

6

(78.1 kHz)

6

1

0

1

1

f

XX

/2

6

f

X

/2

6

(78.1 kHz)

f

X

/2

7

(39.1 kHz)

7

1

1

0

0

f

XX

/2

7

f

X

/2

7

(39.1 kHz)

f

X

/2

8

(19.5 kHz)

8

1

1

0

1

f

XX

/2

8

f

X

/2

8

(19.5 kHz)

f

X

/2

9

(9.8 kHz)

9

1

1

1

0

f

XX

/2

9

f

X

/2

9

(9.8 kHz)

f

X

/2

10

(4.9 kHz)

10

Other than above

Setting prohibited