NEC uPD78P078 User Manual

Page 511

511

CHAPTER 22 INTERRUPT FUNCTIONS

t

SMP

Sampling Clock

INTP0

PIF0

“L”

Because INTP0 level is not active in sampling,

PIF0 output remains at low level.

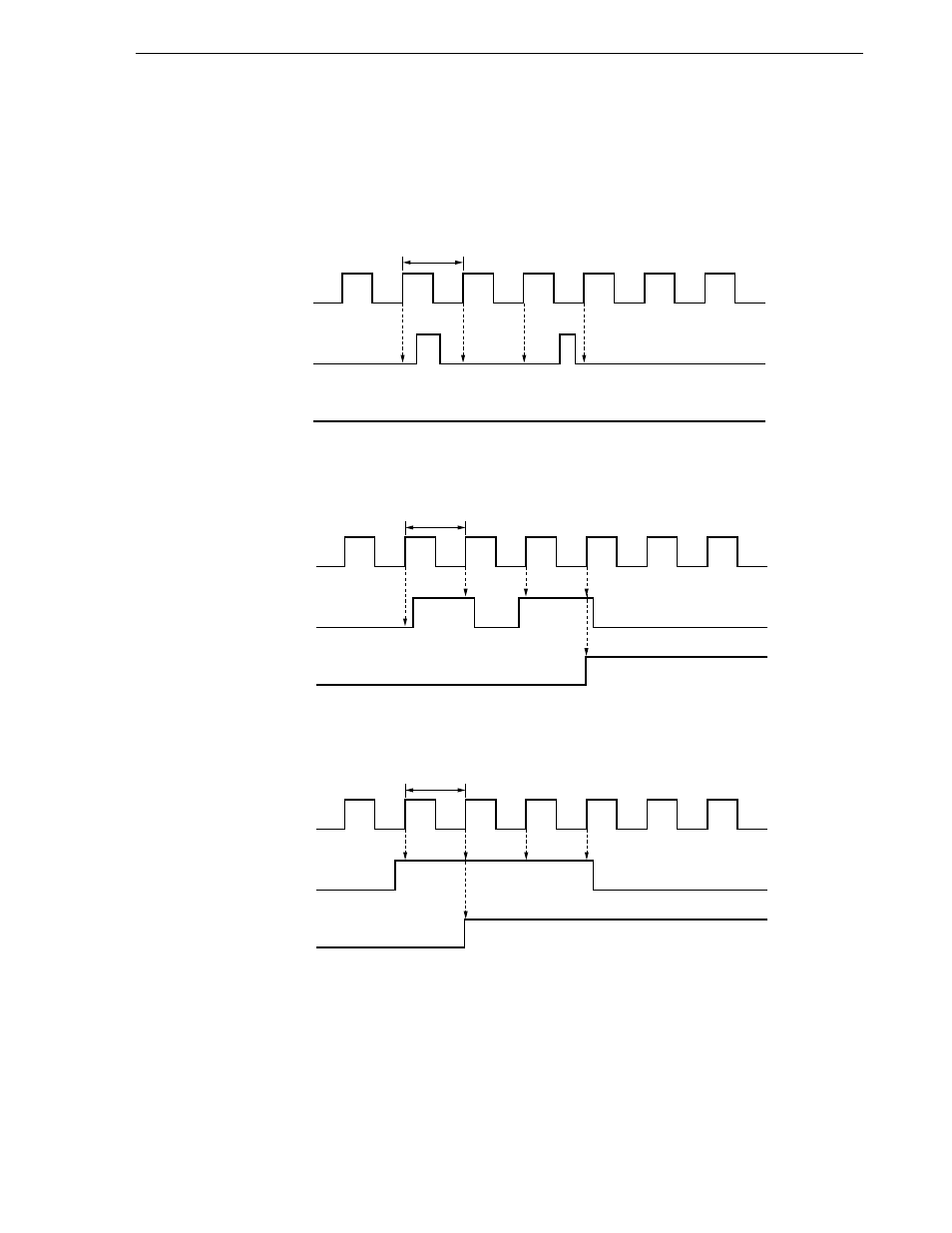

When the setting INTP0 input level is active twice in succession, the noise eliminator sets interrupt request

flag (PIF0) to 1.

Figure 22-8 shows the noise eliminator input/output timing.

Figure 22-8. Noise Eliminator Input/Output Timing (during Rising Edge Detection)

(a) When input is less than the sampling cycle (t

SMP

)

(b) When input is equal to or twice the sampling cycle (t

SMP

)

(c) When input is twice or more than the cycle frequency (t

SMP

)

t

SMP

Sampling Clock

INTP0

PIF0

Because sampling INTP0 level is active twice in succession in <2>,

PIF0 flag is set to 1.

<1>

<2>

t

SMP

Sampling Clock

INTP0

PIF0

When INTP0 level is active twice in succession,

PIF0 flag is set to 1.