NEC uPD78P078 User Manual

Page 402

402

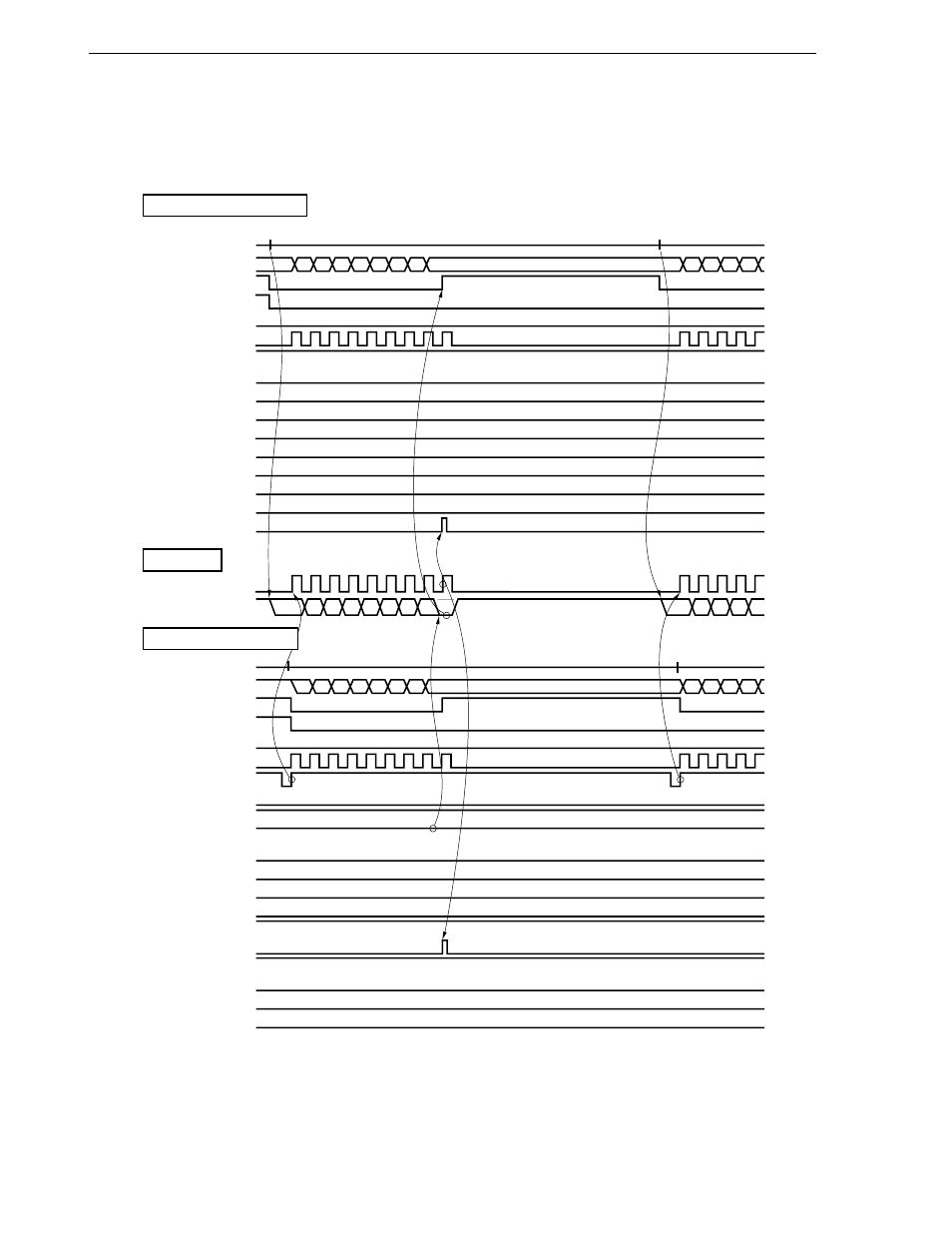

CHAPTER 18 SERIAL INTERFACE CHANNEL 0 (

µ

PD78078Y Subseries)

Figure 18-22. Example of Communication from Master to Slave (with 9-Clock Wait Selected for Both

Master and Slave) (2/3)

(b) Data

L

L

L

L

1

D5 D4 D3 D2 D1 D0 ACK

D6

D7

2

3

4

5

6

7

8

D7 D6 D5 D4 D3

1

2

3

4

5

9

L

L

L

L

L

L

L

SIO0 <- data

SIO0 <- data

H

L

L

L

L

L

L

L

H

H

H

H

SIO0 <- FFH

SIO0 <- FFH

SIO0 write

COI

ACKD

CMDD

RELD

CLD

P27

SCL

SDA0

WUP

BSYE

ACKE

CMDT

RELT

CLC

WREL

SIC

INTCSI0

SIO0 write

COI

ACKD

CMDD

RELD

CLD

P27

WUP

BSYE

ACKE

CMDT

RELT

CLC

WREL

SIC

INTCSI0

CSIE0

P25

PM25

PM27

Processing in master device

Transfer line

Processing in slave device