Sundance Spas ST201 User Manual

Page 86

86

Sundance Technology

ST201

PRELIMINARY draft 2

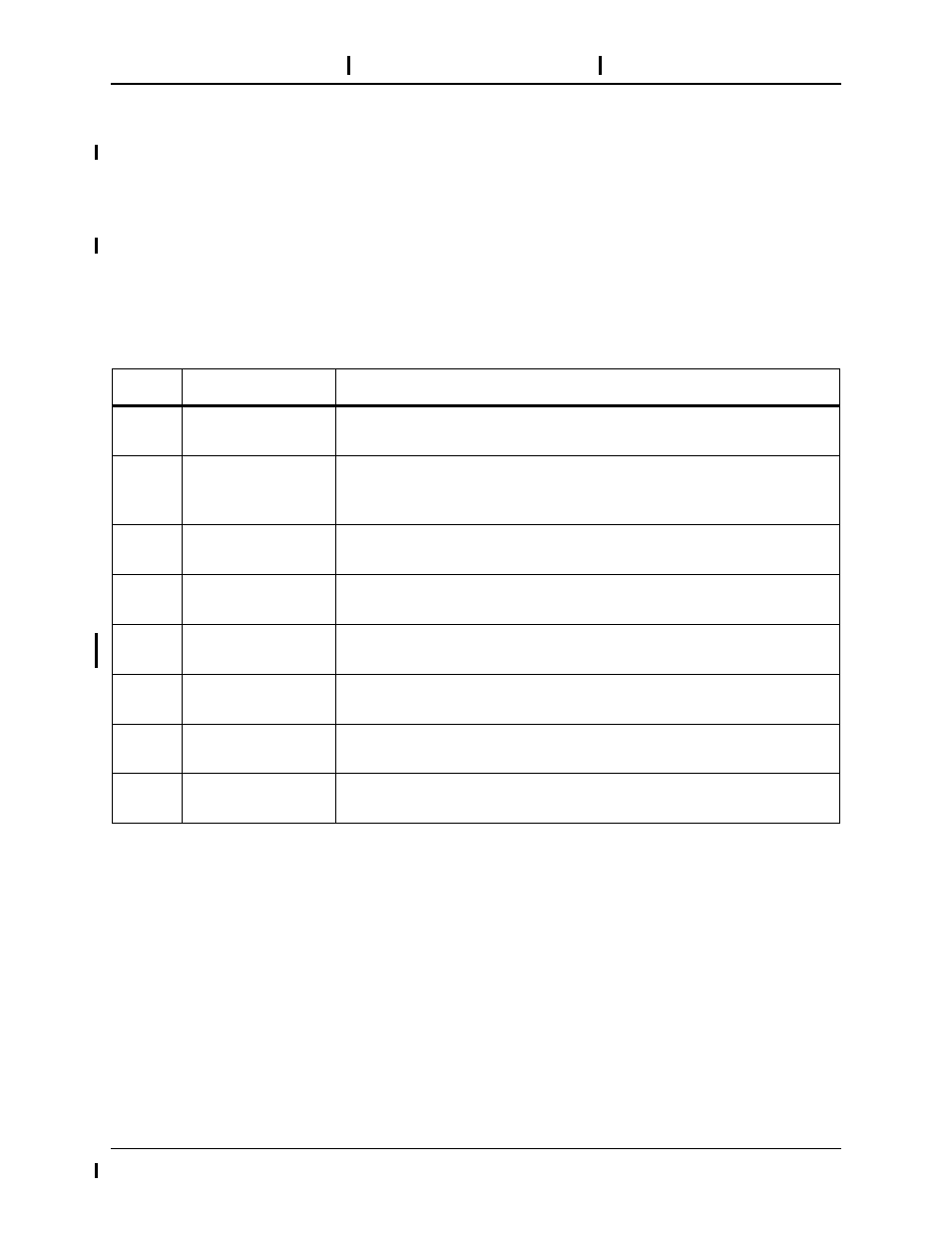

PHYCTRL

Class....................I/O Registers, External Interface Control

Base Address ......IoBaseAddress register value

Address Offset .....0x5e

Access Mode .......Read/Write

Width ...................8 bits

This register contains control bits for the MII Management Interface. The MII Management Interface is

used to access registers in an MII PHY device. The Management Interface is a two-wire serial interface

connecting ST201 to any MII-compliant PHY devices residing on the adapter. The host system operates

the Management Interface by writing and reading bit patterns to the PhyCtrl register which correspond to

the physical waveforms required on the interface signals. For more information on the Management Inter-

face signal protocols, refer to the Media Independent Interface standard of IEEE 802.3u Specification.

BIT

BIT NAME

BIT DESCRIPTION

0

MgmtClk

The MII Management Clock. This bit drives directly the management

clock to the PHY device(s).

1

MgmtData

The MII Management Data bit. When the MgmtDir bit (below) is set,

the value written to this bit is driven onto the MDIO signal. When Mgmt-

Dir is cleared, data being driven by the PMD can be read from this bit.

2

MgmtDir

The MII data direction control bit. Setting this bit causes ST201 to drive

MDIO with the data bit written into MgmtData.

3

DisableClk25

This bit is set to tri-state the CLK25 pin. DisableClk25 is cleared upon

reset.

4

PhyDuplexPolarity

Clearing this read/write bit will cause the PHYDPLXN input pin to be

active low. The default value for this bit upon reset is cleared.

5

PhyDuplexStatus

This read-only bit provides a real-time indication of the duplex status of

the PHY. This bit is set for full duplex operation.

6

PhySpeedStatus

This read-only bit provides a real-time indication of the speed status of

the PHY. This bit is set for 100Mb/s operation.

7

PhyLinkStatus

This read-only bit provides a real-time indication of the twisted-pair

transceiver link. This bit is set for operational link (link status up).