Sundance Spas ST201 User Manual

Page 127

127

Sundance Technology

ST201

PRELIMINARY draft 2

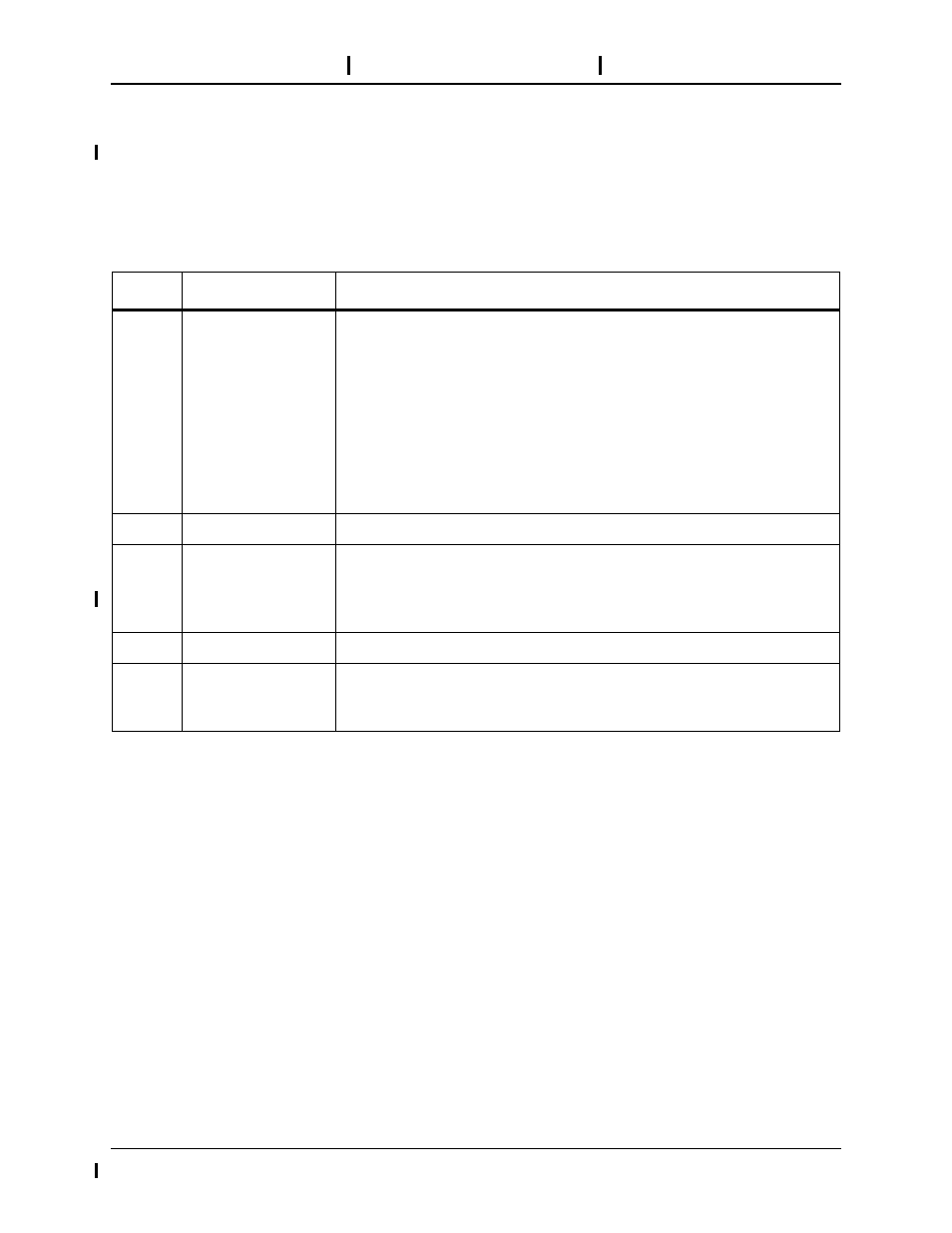

POWERMGMTCTRL

Class....................PCI Configuration Registers, Power Management

Base Address ......PCI device configuration header start

Address Offset .....0x54

Access Mode .......Read/Write

Width ...................16 bits

This register allows control over the power state and the power management interrupts.

BIT

BIT NAME

BIT DESCRIPTION

1..0

PowerState

This read/write field is used to determine or set the ST201’s power

state. The following values are defined:

00: State D0

01: State D1

10: State D2

11: State D3

If PowerState is set to a non-zero value, the ST201 will not respond to

PCI I/O or memory cycles, nor will it be able to generate PCI bus mas-

ter cycles.

7..2

Reserved

Reserved for future use. Should be set to 0.

8

PmeEn

When this read/write bit is set, the ST201 is allowed to report wake

events on the PMEN signal. The specific events which can generate

wake are defined by the WakeEvent I/O register. This bit is loaded

from bit[6] of ConfigParm.

14..9

Reserved

Reserved for future use. Should be set to 0.

15

PmeStatus

This read/clear bit is set to indicate a wake event has occurred. This bit

is set regardless of the value in PmeEn. Writing a one to this bit clears

it. Writing zero has no effect.