Sundance Spas ST201 User Manual

Page 48

48

Sundance Technology

ST201

PRELIMINARY draft 2

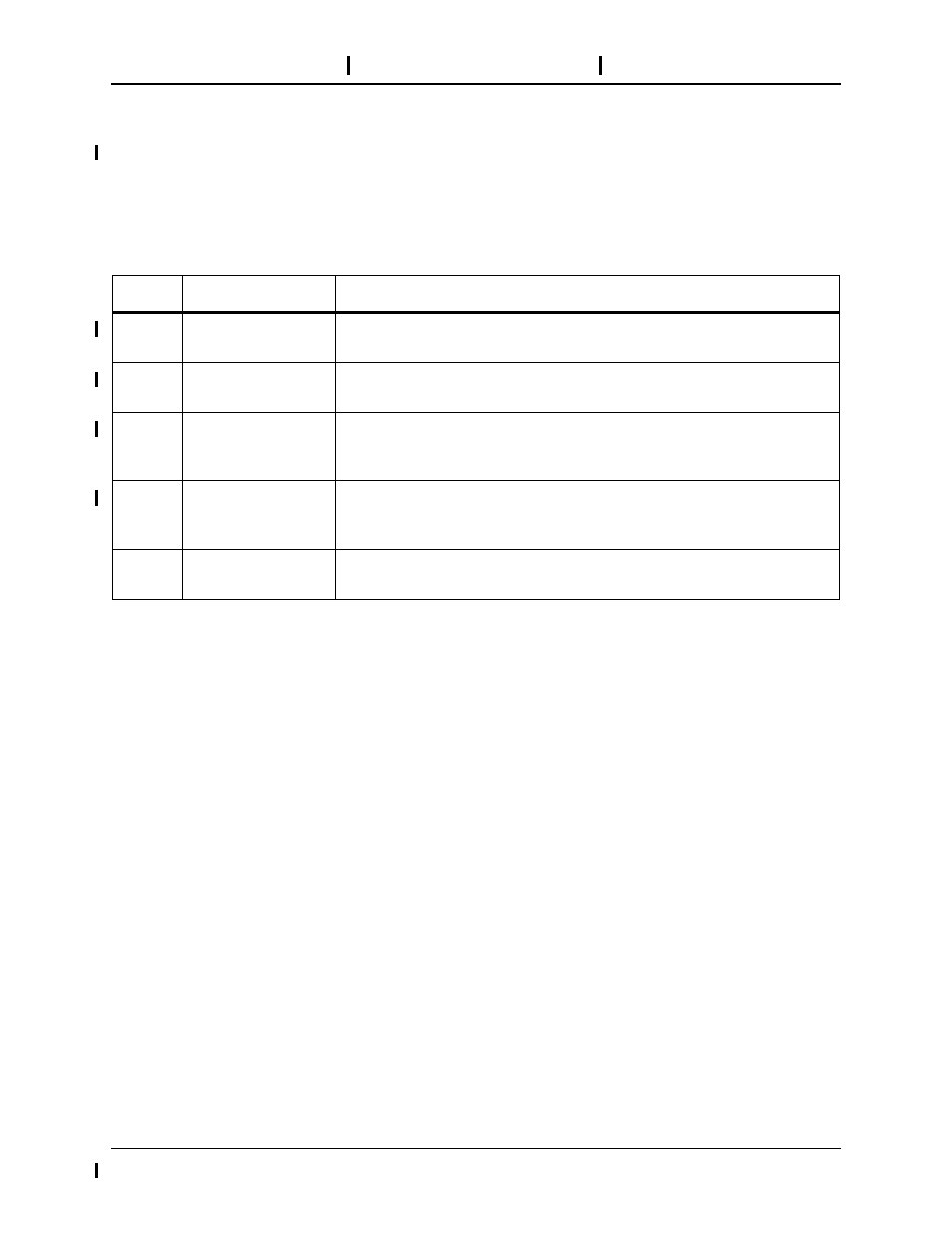

DEBUGCTRL

Class....................I/O Registers, Control and Status

Base Address ......IoBaseAddress register value

Address Offset .....0x1a

Access Mode .......Read/Write

Width ...................16 bits

DebugCtrl selects the functions of the GPIO pins. DebugCtrl is cleared by reset.

BIT

BIT NAME

BIT DESCRIPTION

0

GPIO0Ctrl

This bit controls the GPIO0 pin. When cleared, GPIO0 pin is an input.

When set, GPIO0 pin is an output. This bit is cleared on reset.

1

GPIO1Ctrl

This bit controls the GPIO1 pins. When cleared, GPIO1 pin is an input.

When set, GPIO1 pin is an output. This bit is cleared on reset.

2

GPIO0

When read, this bit shows the status values of the GPIO0 pin. When

written into, this bit will drive the GPIO0 pin if GPIO0Ctrl is set, and

GPIO0 pin functions as an output.

3

GPIO1

When read, this bit shows the status values of the GPIO1 pin. When

written into, this bit will drive the GPIO1 pin if GPIO1Ctrl is set, and

GPIO1 pin functions as an output.

15..4

Reserved

Reserved for future use. Should be set to 0.