Sundance Spas ST201 User Manual

Page 7

7

Sundance Technology

ST201

PRELIMINARY draft 2

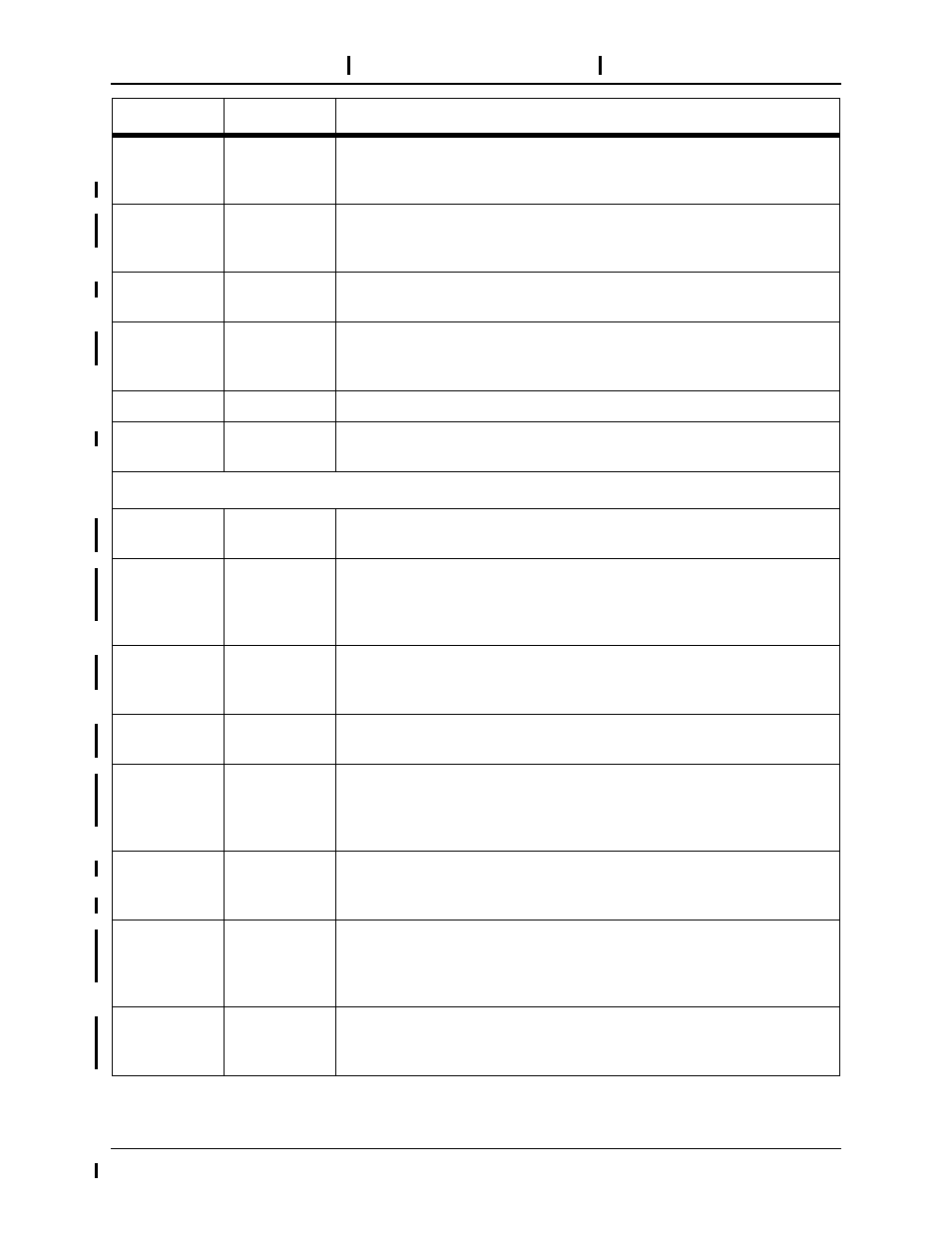

TRDYN

IN/OUT

Target Ready, asserted LOW. A bus target asserts TRDYN to indicate

valid read data phases, and to indicate it is ready to accept data during

write data phases. A bus master will monitor TRDYN.

DEVSELN

IN/OUT

Device Select, asserted LOW. The ST201 asserts DEVSELN when it is

selected as a target during a bus transaction. It monitors DEVSELN for

any target to acknowledge a bus transaction initiated by the ST201.

STOPN

IN/OUT

Stop, asserted LOW. STOPN is driven by the slave target to inform the

bus master to terminate the current transaction.

PERRN

IN/OUT

Parity Error, asserted LOW. The ST201 asserts PERRN when it

checks and detects a bus parity errors. When it is generating PAR out-

put, the ST201 monitors for any reported parity error on PERRN.

SERRN

OUTPUT

System Error, asserted LOW.

VDET

INPUT

Power Detect. The ST201 detects PCI bus power supply loss when

VDET is LOW.

MII INTERFACE

TXD[3..0]

OUTPUT

Transmit Data. This is the 4-bit transmit data, from the transmit MAC to

the physical layer device. TXD[3..0] are synchronized to the TXCLK.

TXEN

OUTPUT

Transmit Enable. When asserted, TXEN indicates to the PHY that

TXD[3..0] carry valid transmit data. TXEN is asserted with the first nib-

ble of the preamble until the last nibble of the frame data. TXEN is syn-

chronous with TXCLK.

TXCLK

INPUT

Transmit Clock. TXCLK is a continuous clock supplied by the PHY to

synchronize the TXD transfer. Nominal rate of TXCLK is 25MHz for

100Mbps PHY and 2.5MHz when the PHY operates at 10Mbps.

RXD[3..0]

INPUT

Receive Data. RXD[3..0] is the receive data from the PHY. RXD[3..0]

are synchronized to RXCLK.

RXCLK

INPUT

Receive Clock. RXCLK provides the timing reference for RXD, RXER,

and RXDV signals. It is supplied by the PHY based on the receive

clock recovery circuit. Nominal rate for RXCLK is 25MHz (for

100Mbps) and 2.5MHz (for 10Mbps).

RXER

INPUT

Receive Error. RXER is an indication from the PHY when it detects

coding errors, or other types of PHY layer errors during frame data

reception. RXER is synchronous with RXCLK.

RXDV

INPUT

Receive Data Valid. RXDV signals valid frame data is present on the

RXD[3..0] pins. The PHY asserts RXDV before the SFD, and de-

asserts it after the last data nibble of the frame. RXDV is synchronous

with RXCLK.

CRS

INPUT

Carrier Sense. CRS is asserted by the PHY to signal a non-idle

medium, with either transmit or receive activity detected. CRS is asyn-

chronous to RXCLK and TXCLK.

PIN NAME

PIN TYPE

PIN DESCRIPTION

TABLE 2: ST201 Pin Descriptions