Sundance Spas ST201 User Manual

Page 46

46

Sundance Technology

ST201

PRELIMINARY draft 2

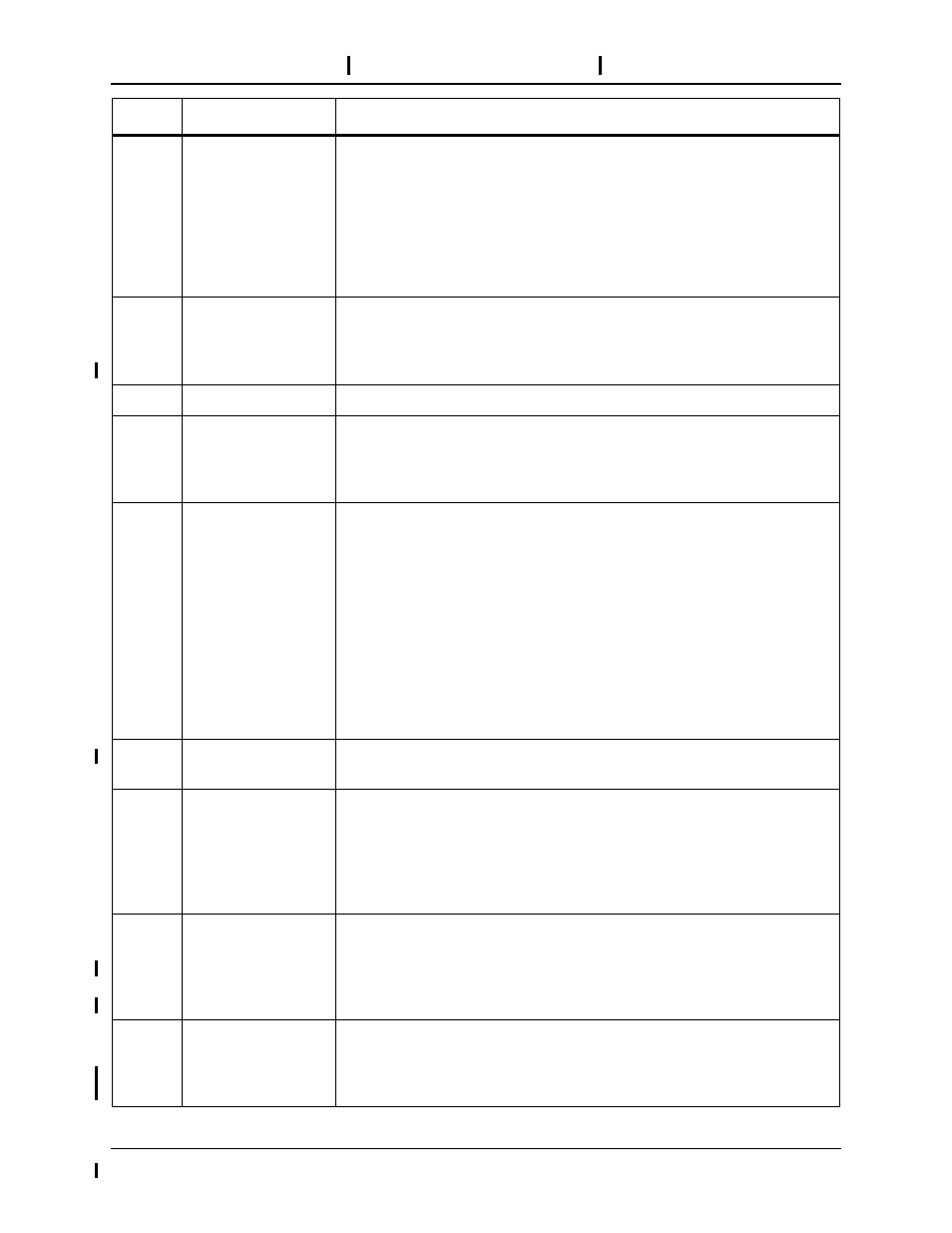

10..8

ForcedConfig

These bits are used to place the ST201 into Forced Configuration

mode. The bit values are latched in from ED[2..0] pins with a logic

inversion at the end of RSTN or power on reset.

000: no forced configuration

001: forced configuration mode 1

010-111: reserved

Note: When ForcedConfig[10] is set, the ST201 will use an alternate

DeviceID and VendorID.

11

D3ResetDisable

This read/write bit, when set, indicates that the ST201 is configured for

operation in an AMD-style (pre-ACPI) Wake-On-LAN environment.

Specifically, when the ST201 is in the D3 power state, assertion of PCI

RSTN will not reset the ST201. It is cleared upon reset.

12

Reserved

Reserved for future use. Should be set to 0.

13

SpeedupMode

This read/write bit is used for simulation only. When set, it indicates a

speed-up mode to decrease simulation time. The bit value is latched in

from ED5 pin with a logic inversion at the end of RSTN or power on

reset.

14

LEDMode

This bit is used to control the LED outputs. When cleared (default after

reset), the LED outputs are in mode 0; when set, the LED outputs are

in mode 1.

LEDPWRN: Mode 0: steady ON when power is applied, flashing when

frames are being transmitted. Mode 1: ON all the time.

LEDLNKN: Mode 0: steady ON when link is up, and flashing when

frames are being received. Mode 1: steady ON when link is up, and

flashing when frames are being transmitted or received.

LEDDPLXN: Mode 0/1: steady ON when PHY is in full duplex mode,

and flashing when collisions are being detected.

LEDSPDN: Mode 0/1: steady ON when link speed is 100mb/s, and

OFF when link speed is 10Mb/s.

15

RstOutPolarity

When set, RSTOUT is asserted high. When cleared, RSTOUT is

asserted low.

16

GlobalReset

This is a self-clearing global reset bit for the entire ST201. This bit con-

trols reset to various logic blocks depending on the values of the selec-

tion bits [24..19]. The ST201 should be re-initialized after a

GlobalReset. The registers in the PCI configuration space are not reset

by the GlobalReset; they are handled by the Power On Reset Test rou-

tine executed by the host.

17

RxReset

When set, will reset receive logic throughout the ST201, including net-

work interface receive logic, RxFIFO control logic, and RxDMA Logic if

the corresponding selection bits [21..19] are set. This bit is self-clear-

ing. The RxReset should not be used after initialization except to

recover from receive errors such as a RxFIFO under run.

18

TxReset

When set, will reset transmit logic throughout the ST201, including net-

work interface transmit logic, TxFIFO control logic, and TxDMA Logic,

if the corresponding selection bits [21..19] are set. This bit is self-clear-

ing. The TxReset is required after a transmit under run error.

BIT

BIT NAME

BIT DESCRIPTION