Sundance Spas ST201 User Manual

Page 109

109

Sundance Technology

ST201

PRELIMINARY draft 2

CONFIGSTATUS

Class....................PCI Configuration Registers, Configuration

Base Address ......PCI device configuration header start

Address Offset .....0x06

Access Mode .......Read/Write

Width ...................16 bits

This register is used to record status information for PCI bus events. Read/write bits in the register can

only be reset, not set, by writing to this register. Bits are reset by writing a one to that bit position.

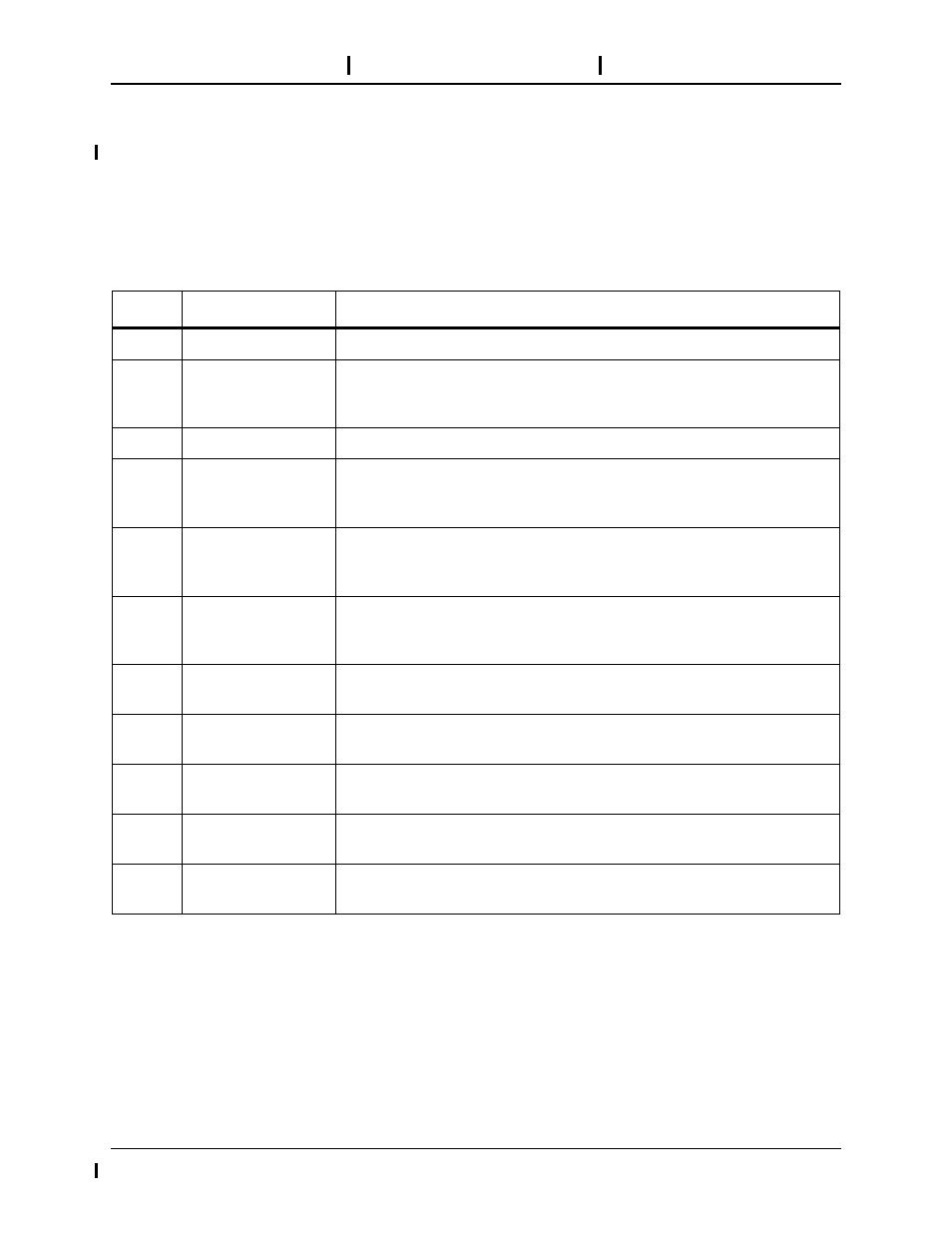

BIT

BIT NAME

BIT DESCRIPTION

3..0

Reserved

Reserved for future use. Should be set to 0.

4

Capabilities

This read-only bit is always set, indicating the existence of a list of

extended capabilities registers. The CapPtr register points to the start

of the list.

6..5

Reserved

Reserved for future use. Should be set to 0.

7

FastBackToBack

This read-only bit, when set, indicates that the adapter, as a Target,

supports fast back-to-back transactions as defined by the criteria in the

section 3.4.2 of the PCI specification.

8

DataParityRe-

ported

The adapter sets this bit when, as a master, it detects the PERRN sig-

nal asserted, and the ParityErrorResponse bit is set in the ConfigCom-

mand register.

10..9

DevselTiming

This read-only field is used to encode the slowest time with which the

adapter asserts the DEVSELN signal. ST201-based adapters return

01b, indicating that they support “medium” speed DEVSELN assertion.

11

SignaledTargetA-

bort

The adapter sets this bit when it terminates a bus transaction with tar-

get-abort.

12

ReceivedTargetA-

bort

The adapter sets this bit when, operating as a bus master, its bus

transaction is terminated with target-abort.

13

ReceivedMaster-

Abort

The adapter sets this bit when, operating as a bus master, its bus

transaction is terminated with master-abort.

14

SignaledSystemEr-

ror

This bit is set whenever the adapter asserts SERRN.

15

DetectedParityEr-

ror

The adapter sets this bit when it detects a parity error, regardless of

whether parity error handling is enabled.