Table 7. main board components – Intel SR9000MK4U User Manual

Page 41

Intel

®

Server System SR9000MK4U Product Guide

19

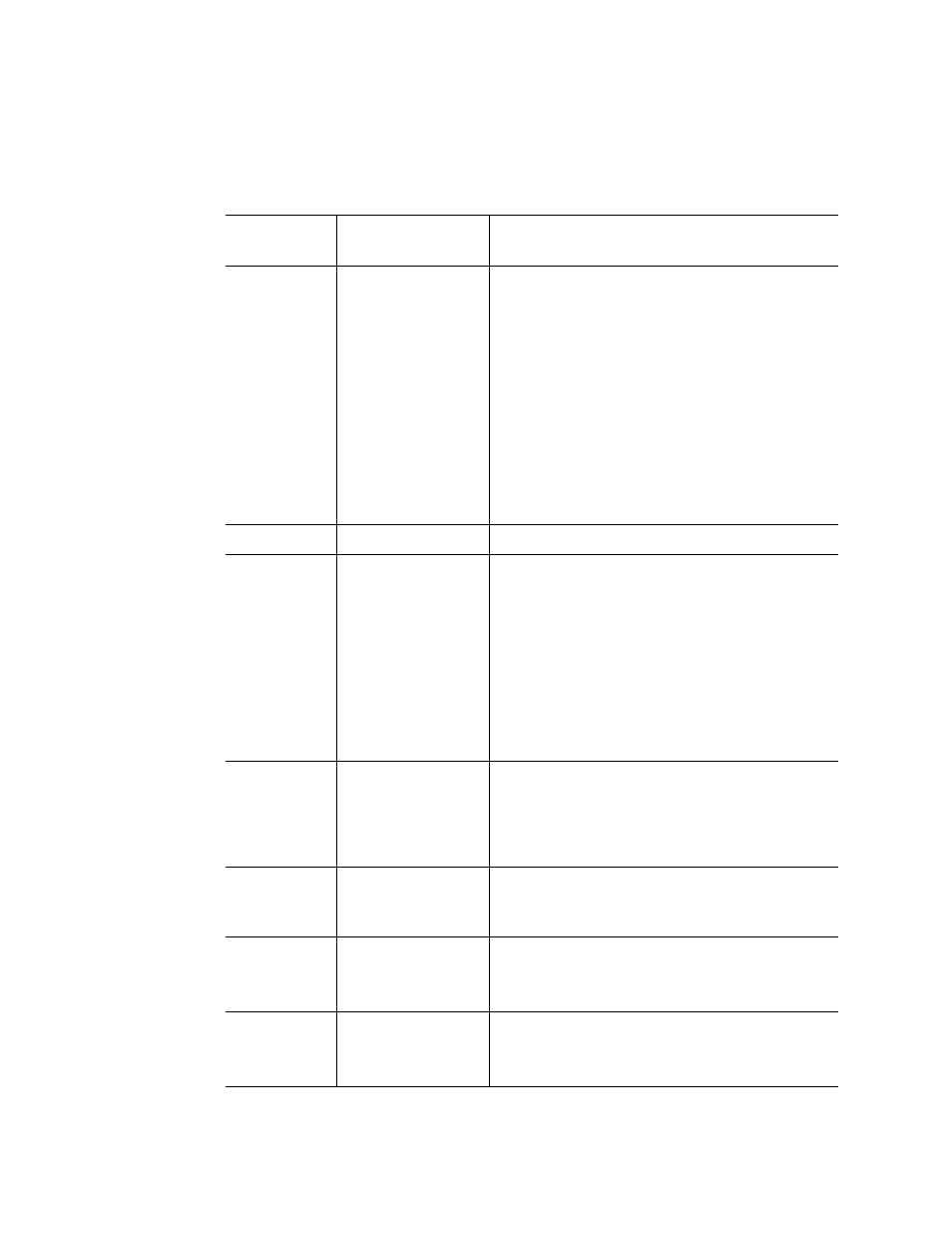

Table 7. Main Board Components

Board

Location

Component

Description

P1/P2

Hitachi* NDC

Node Controller:

•

One Front Side Bus

–

533/667 MHz FSB support

–

Two processors per bus

•

Four interfaces connecting to the memory

controller

•

Three x8 PCI Express* ports

•

Proprietary high-speed interface to link between

two node controllers

•

Optimized design for 667 MHz FSB to achieve

low memory access latency

•

Broadcast-based cache coherence control to

minimize snoop transaction

P3

Intel

®

ESB2

Enterprise South Bridge

P4

Intel

®

6700PXH

64-bit PCI Hub:

•

PCI bridging functions between the PCI Express

interface and the PCI Bus

•

One PCI Express* interface (primary bus)

•

x8 and x4 modes operation

•

Maximum 2 GB/s in each direction

simultaneously

•

Two PCI / PCI-X* bus interfaces (secondary bus)

•

PCI 2.3-compliant

•

PCI-X 1.0b-compliant

P5

Intel

®

82563

Physical Layer Transceiver (PHY) component

designed for 10/100/1000 Mbps operation:

•

IEEE 802.3 (10BASE-T), IEEE 802.3u

(100BASE-TX), IEEE 802.3ab (1000BASE-T)

•

Dual port

P6

Intel

®

82551QM

Fast Ethernet PCI bus controller:

•

IEEE 802.3 (10BASE-T), IEEE 802.3u

(100BASE-TX), 32-bit PCI bus master interface

P7

ATI* ES1000

Graphics processing unit:

•

2D graphics accelerator

•

PCI bus interface (PCI 2.2 compliant, 33 MHz)

P8

VRAM

64 MB VRAM for ATI ES1000:

•

Max resolution: Up to 1280 x 1024, 85 Hz

•

Max color depth: Up to 32 bpp true color