IBM B50 User Manual

Page 88

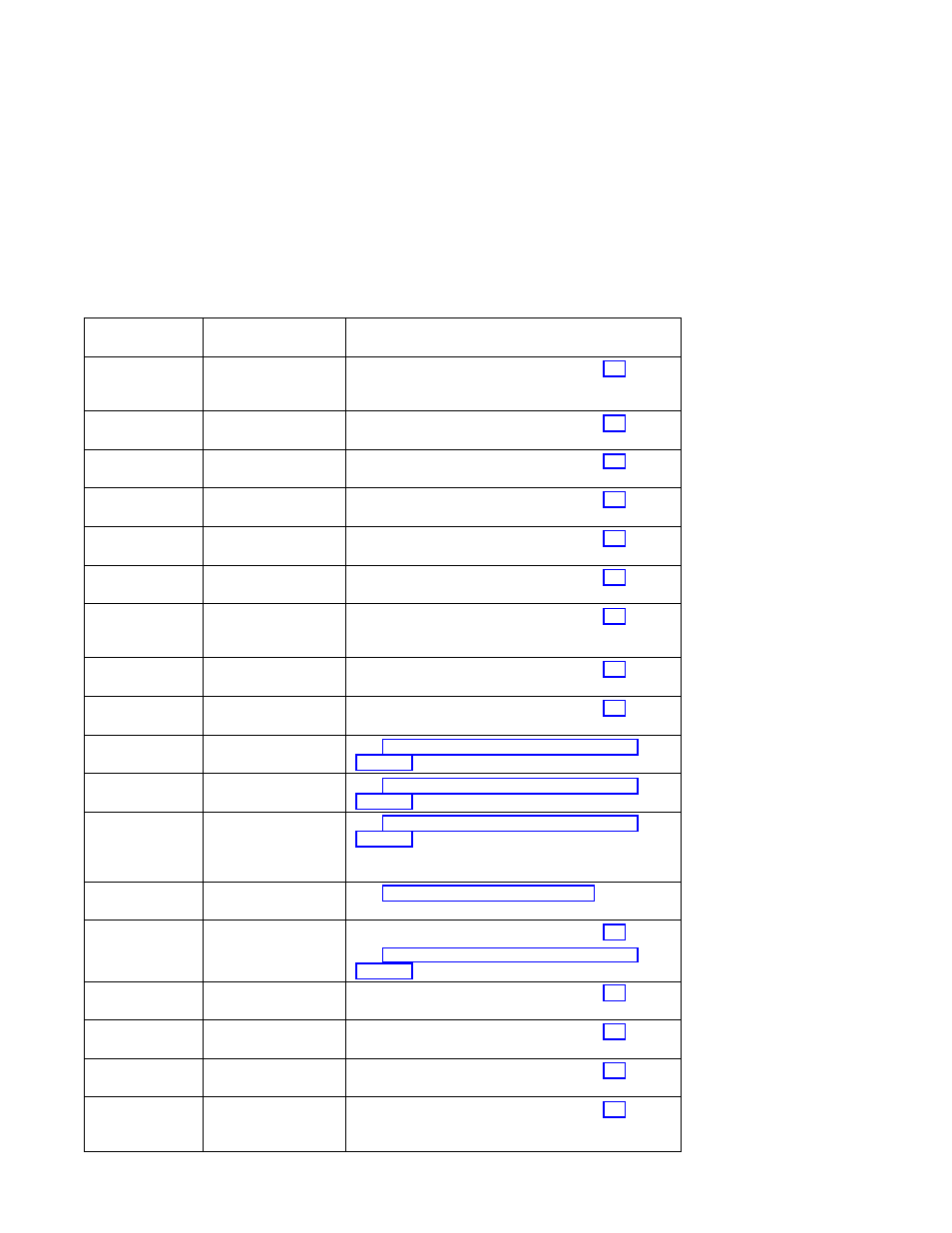

Checkpoint

(hex)

Description

Repair Action

E207

Setup Data gather

mode and 64/32-bit

mode on PCG

Replace system board (see note 3 on page 2-1).

E208

Assign bus number

on PCG

Replace system board (see note 3 on page 2-1).

E209

Assign PCI I/O

addresses on PCI

Replace system board (see note 3 on page 2-1).

E20A

Assign PCI I/O

addresses on PCG

Replace system board (see note 3 on page 2-1).

E20B

Check MCERs stuck

at fault

Replace system board (see note 3 on page 2-1).

E20C

Testing L2 cache

Replace system board (see note 3 on page 2-1).

E210

Processors L1 data

cache array test

fails. System Hangs.

Replace system board (see note 3 on page 2-1).

E211

IPL ROS CRC

checking

Replace system board (see note 3 on page 2-1).

E212

Processor POST

Replace system board (see note 3 on page 2-1).

E213

Initial memory

configuration

See “MAP 1240: Memory Problem Resolution” on

page 2-9

E214

Memory test

See “MAP 1240: Memory Problem Resolution” on

page 2-9

E216

Copy ROS into

RAM. Set up

Translation and C

environment

See “MAP 1240: Memory Problem Resolution” on

page 2-9

E21A

System has some

good memory

See “Unresolved problems” on page 3-26

E220

Final memory

configuration

Replace system board (see note 3 on page 2-1).

See “MAP 1240: Memory Problem Resolution” on

page 2-9

E240

Set up Winbond ISA

bridge

Replace system board (see note 3 on page 2-1).

E241

Reset PCI Bus

Replace system board (see note 3 on page 2-1).

E242

Initialize ISA DMA

channel

Replace system board (see note 3 on page 2-1).

E243

Set up Grackle

configuration

registers

Replace system board (see note 3 on page 2-1).

3-24

7046 Model B50 Service Guide