Figure3.7 rise and fall time test conditions, Rise and fall time test conditions – Avago Technologies LSI53C180 User Manual

Page 48

3-14

Specifications

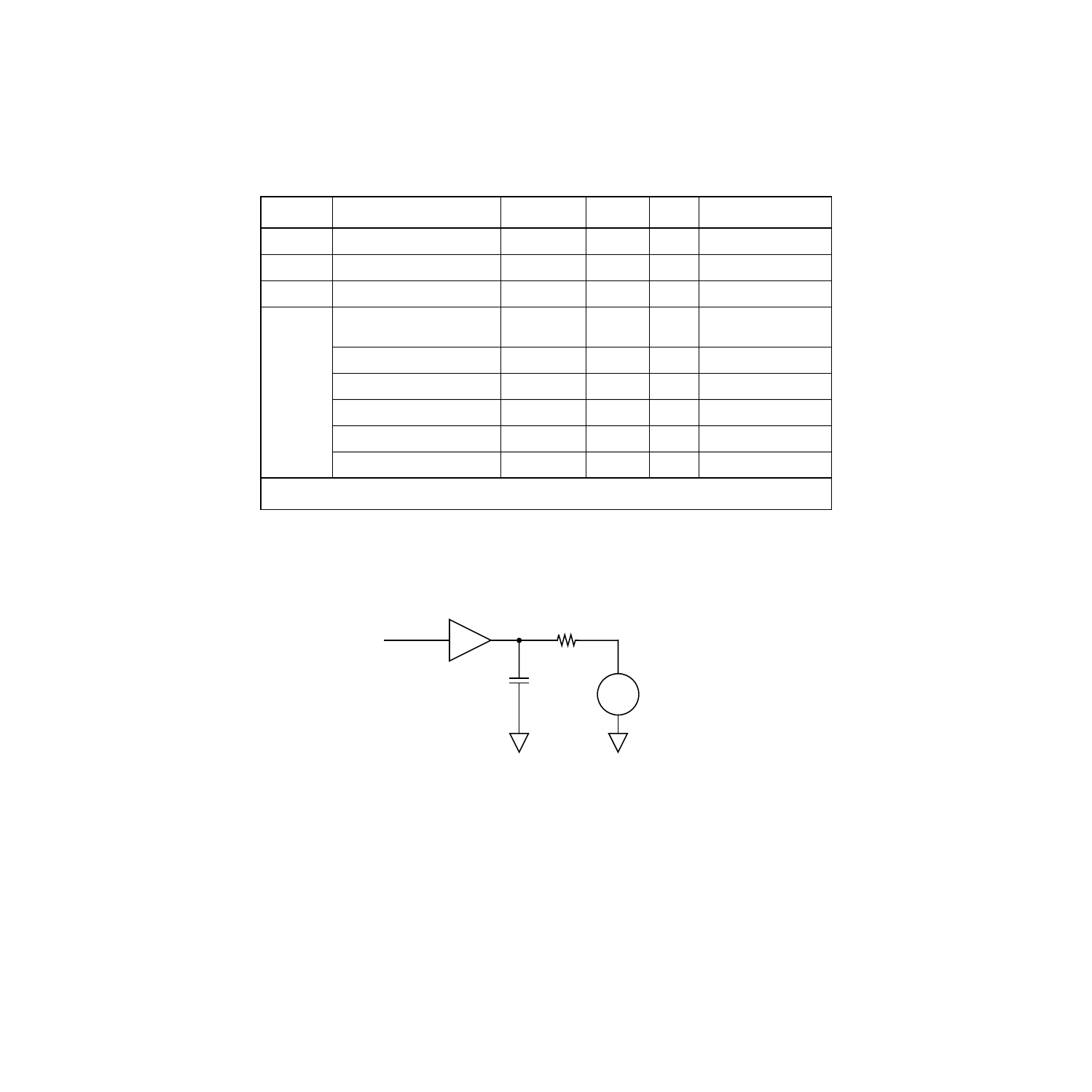

Figure 3.7

Rise and Fall Time Test Conditions

t

F

Fall time, 90% to 10%

4.0

18.5

ns

dV

H

/dt

Slew rate, LOW to HIGH

0.15

0.50

V/ns

dV

L

/dt

Slew rate, HIGH to LOW

0.15

0.50

V/ns

ESD

Electrostatic discharge

2

–

kV

MIL-STD-883C;

3015-7

Latch-up

100

–

mA

–

Filter delay

20

30

ns

Ultra filter delay

10

15

ns

Ultra3 filter delay

x

x

ns

Extended filter delay

40

60

ns

1. These values are guaranteed by periodic characterization; they are not 100% tested on every device.

2. Active negation outputs only: Data, Parity, SREQ/, SACK/. (Minus Pins) SCSI mode only.

3. Single pin only; irreversible damage may occur if sustained for one second.

4. SCSI RESET pin has 10 k

Ω

pull-up resistor.

Table 3.15

TolerANT Technology Electrical Characteristics

1

(Cont.)

Symbol

Parameter

Min

Max

Units

Test Conditions

(Sheet 2 of 2)

20 pF

47

Ω

2.5 V

+

−

- MGA-725M4 (4 pages)

- MGA-71543 (4 pages)

- MGA-71543 (3 pages)

- MGA-82563 (6 pages)

- 3ware SAS 9750-8i (48 pages)

- 3ware 9690SA-8I (Channel) (138 pages)

- 3ware 9690SA-8I (Channel) (380 pages)

- 3ware SAS 9750-8i (29 pages)

- 3ware 9550SXU-8LP (Channel) (149 pages)

- 3ware 9550SXU-8LP (Channel) (40 pages)

- 3ware 9650SE-8LPML (Channel) (45 pages)

- 3ware 9690SA-8I (Channel) (27 pages)

- 3ware 9690SA-8I (Channel) (361 pages)

- 6160 SAS Switch (2 pages)

- MegaRAID SAS 9380-8e (43 pages)

- Cache Protection for RAID Controller Cards (139 pages)

- Cache Protection for RAID Controller Cards (13 pages)

- MegaRAID SAS 9271-8iCC (13 pages)

- MegaRAID SAS 9361-8i (13 pages)

- MegaRAID SAS 9266-8i (12 pages)

- MegaRAID SAS 9266-8i (20 pages)

- MegaRAID SAS 9271-8iCC (26 pages)

- MegaRAID SafeStore Software (502 pages)

- MegaRAID SAS 9285-8ecv (80 pages)

- MegaRAID SAS 9285-8ecv (92 pages)

- MegaRAID SAS 0260CV-4i (49 pages)

- MegaRAID SAS 9271-8i (8 pages)

- MegaRAID SAS 0260CV-4i (72 pages)

- MegaRAID SAS 0260CV-4i (64 pages)

- MegaRAID SAS 9361-8i (7 pages)

- MegaRAID SAS 9341-8i (8 pages)

- MegaRAID SAS 9380-4i4e (7 pages)

- MegaRAID SAS 9380-8e (7 pages)

- MegaRAID SAS 0260CV-4i (28 pages)

- MegaRAID SAS 9240-8i (4 pages)

- MegaRAID SAS 9280-24i4e (14 pages)

- MegaRAID SAS 9280-24i4e (16 pages)

- MegaRAID SAS 9260-16i (12 pages)

- MegaRAID SAS 9260-8i (4 pages)

- MegaRAID SafeStore Software (8 pages)

- MegaRAID SAS 9280-8e (22 pages)

- MegaRAID SAS 9261-8i (4 pages)

- MegaRAID SAS 9285-8e (12 pages)

- MegaRAID SAS 9280-16i4e (12 pages)

- MegaRAID SAS 9280-4i4e (4 pages)