Ethernet mac/phy (u4), Serial port connectors (j19 & j27), Serial port connectors (j19 & j27) –14 – Altera Nios Development Board User Manual

Page 22

2–14

Altera

Corporation

Nios Development Board Reference Manual, Stratix II Edition

July 2005

Ethernet MAC/PHY (U4)

Ethernet

MAC/PHY (U4)

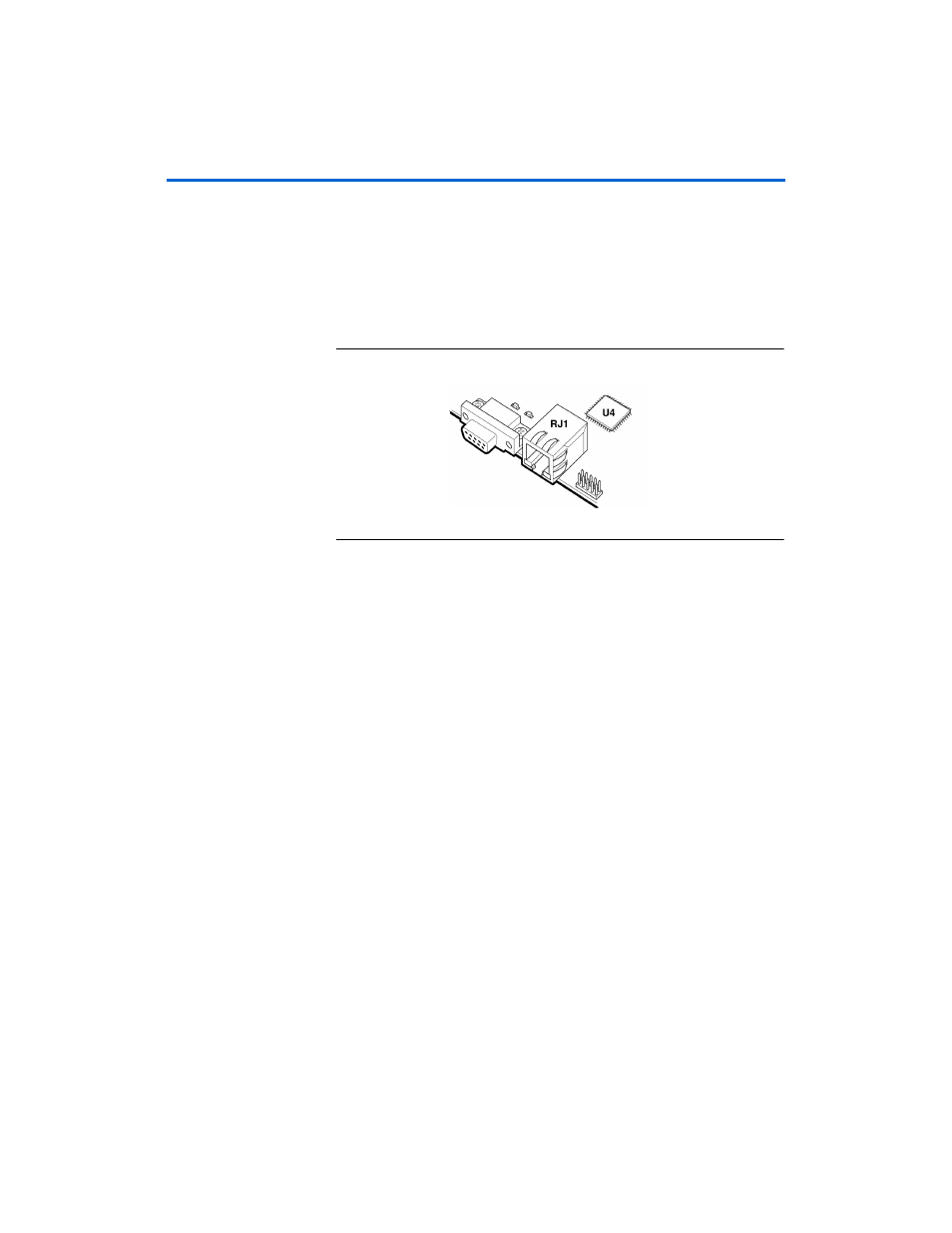

The LAN91C111 (U4) is a mixed signal analog/digital device that

implements protocols at 10 Mbps and 100 Mbps. The control pins of U4

are connected to the Stratix II device so that Nios II systems can access

Ethernet via the RJ-45 connector (RJ1).See

. The

Nios II development kit includes hardware and software components

that allow Nios II processor systems to communicate with the

LAN91C111 Ethernet device.

Figure 2–4. Ethernet RJ-45 Connector

The Ethernet MAC/PHY device shares address and data connections

with the flash memory and the SRAM chips. For shared bus information,

see

f

Refer to www.smsc.com for detailed information about the LAN91C111

device.

Serial Port

Connectors (J19

& J27)

J19 and J27 are standard DB-9 serial connectors. These connectors are

typically used for communication with a host computer using a standard,

9-pin serial cable connected to (for example) a COM port. Level-shifting

buffers (U52 and U58) are used between J19 & J27 and the Stratix II

device, because the Stratix II device cannot interface to RS-232 voltage

levels directly.

J19 and J27 are able to transmit all RS-232 signals. Alternately, the

Stratix II design may use only the signals it needs, such as J19’s RXD and

TXD

. LEDs are connected to the RXD and TXD signals, giving a visual

indication when data is being transmitted or received.

and

show the pin connections between the serial connectors and

the Stratix II device.