Transceiver connector (optional), High-speed mezzanine cards – Altera Cyclone IV GX FPGA Development Board User Manual

Page 37

Chapter 2: Board Components

2–29

Components and Transceiver Interfaces

May 2013

Altera Corporation

Cyclone IV GX FPGA Development Board

Reference Manual

lists the Ethernet PHY interface component reference and manufacturing

information.

Transceiver Connector (Optional)

The HSMC port B interface (J2) uses the same transceivers as the PCIe interface. A

capacitor or resistor stuffing option is used to select the transceivers for either the

PCIe or the HSMC port B interface. The default stuffing option is the PCIe interface.

lists the capacitor or resistor stuffing option to enable either the PCIe

interface or the HSMC port B interface. The multiplexer capacitors are 0.1

μF and the

multiplexer resistors are 0

Ω.

High-Speed Mezzanine Cards

The development board contains two HSMC interfaces—port A and port B. The

HSMC port A interface supports both single-ended and differential signaling while

the HSMC port B interface only supports single-ended signaling. The HSMC interface

also allows JTAG, SMB, clock outputs and inputs, as well as power for compatible

HSMC cards. The HSMC is an Altera-developed open specification, which allows you

to expand the functionality of the development board through the addition of

daughtercards.

f

For more information about the HSMC specification such as signaling standards,

signal integrity, compatible connectors, and mechanical information, refer to the

manual.

U21.74

100 Mbps connection speed LED

ENET_LED_LINK100

1.8-V CMOS

—

U21.73

1000 Mbps connection speed LED

ENET_LED_LINK1000

—

U21.70

Duplex or collision LED

ENET_LED_DUPLEX

—

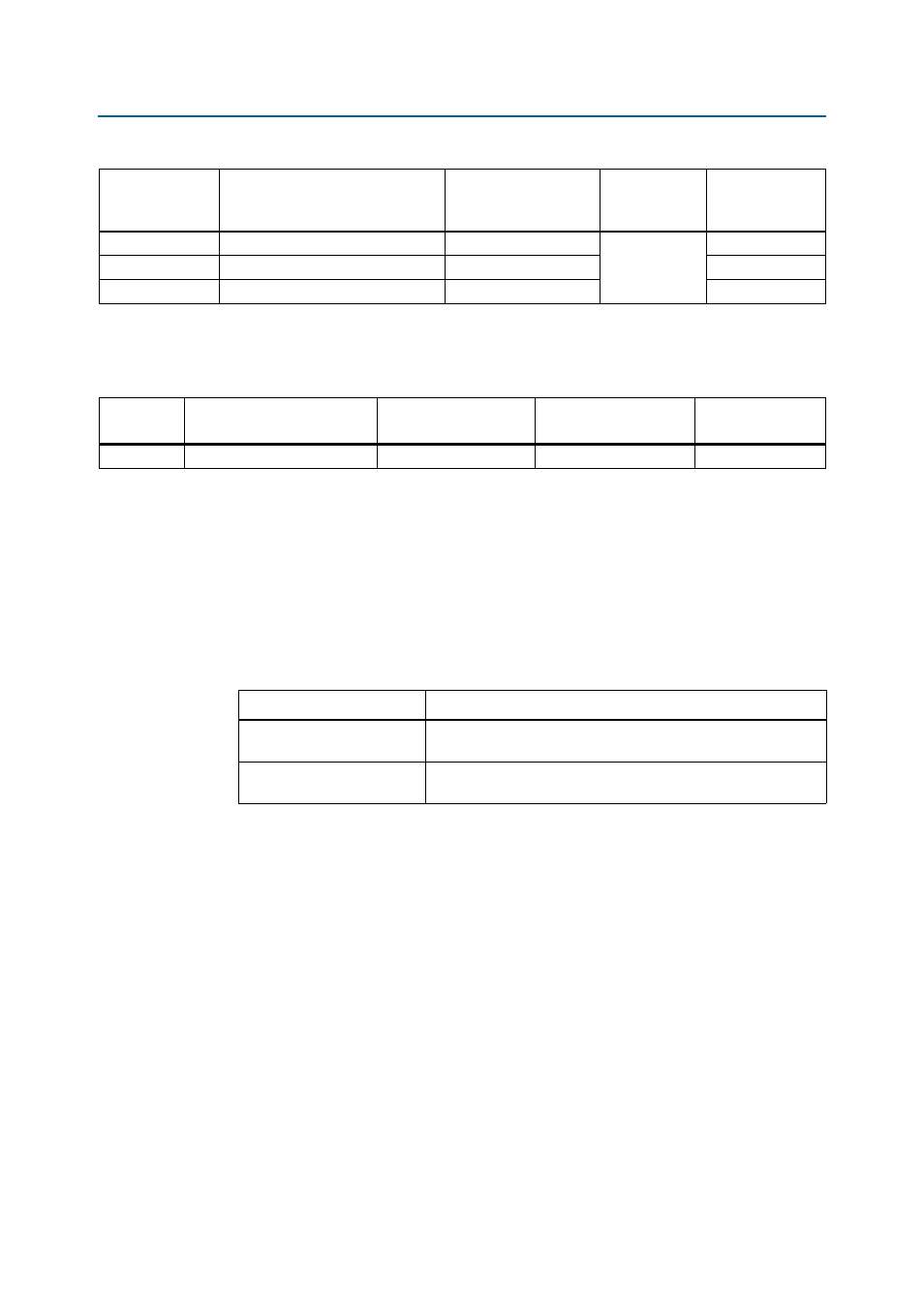

Table 2–30. Ethernet PHY Pin Assignments, Signal Names and Functions

Board Reference

Description

Schematic Signal Name

I/O Standard

Cyclone IV GX

Device

Pin Number

Table 2–31. Ethernet PHY Component Reference and Manufacturing Information

Board

Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U21

Ethernet PHY BASE-T device

Marvell Semiconductor

88E1111-B2-CAAIC000

Table 2–32. Multiplexer Location for PCIe Interface and HSMC Port B Interface

Selection

Multiplexer Location

PCIe interface

Populate C324, C326, C328, C330, C341, C343, C345, C347, R80,

R81, R84, R86, R88, R89, R92, R96

HSMC port B interface

Populate C323, C325, C327, C329, C340, C342, C344, C346, R82,

R83, R85, R87, R90, R91, R93, R97