Altera Transceiver Signal Integrity Development Kit, Stratix IV GT Edition User Manual

Page 18

2–8

Chapter 2: Board Components

Featured Device: Stratix IV GT Device

Transceiver Signal Integrity Development Kit,

November 2011

Altera Corporation

Stratix IV GT Edition Reference Manual

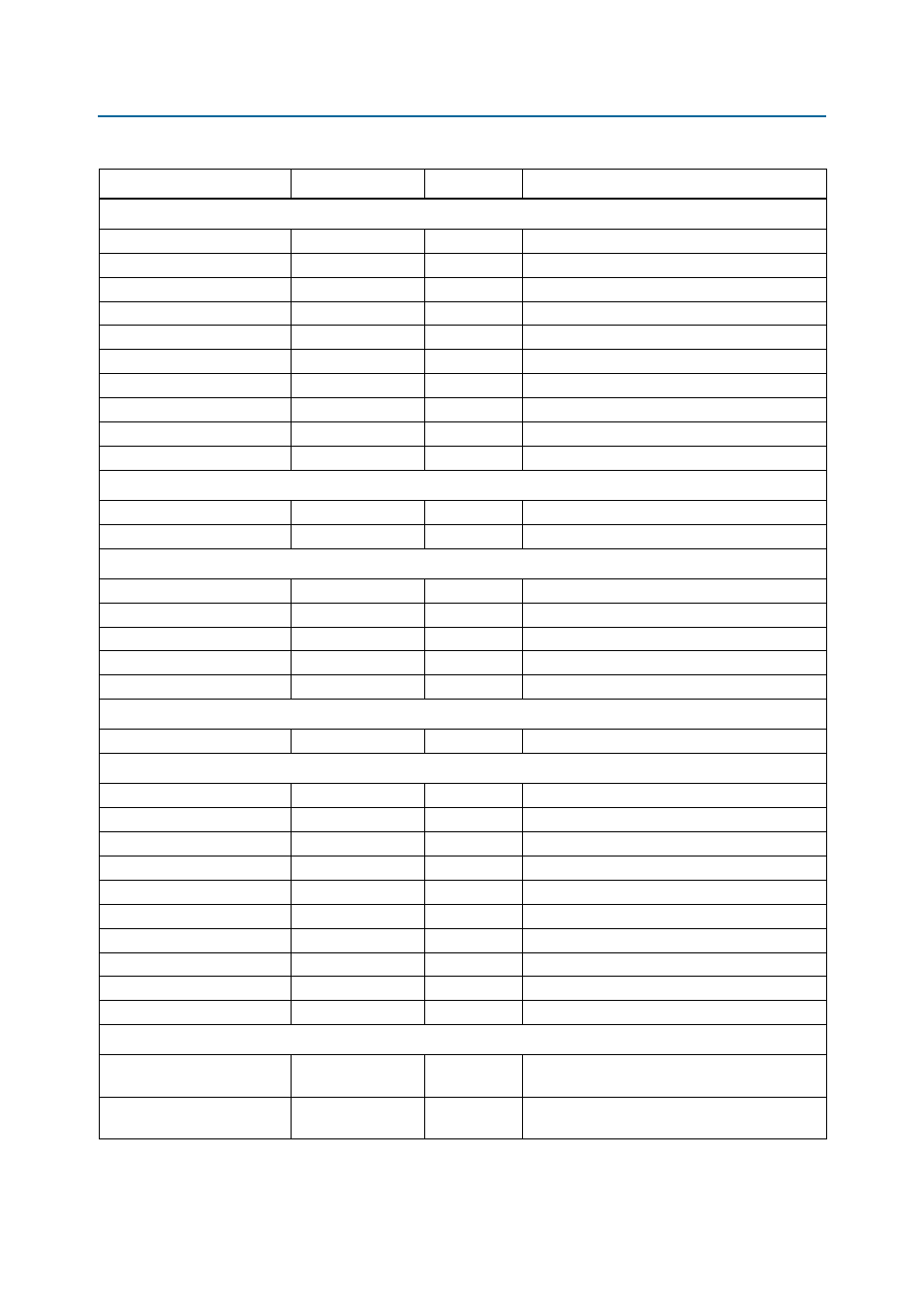

Flash Memory

ADDR[25:0]

2.5-V CMOS output

26

Flash Address Bus

DATA[15:0]

2.5-V CMOS inout

16

Flash Data Bus

FLASH_CEn

2.5-V CMOS output

1

Flash Chip Enable

FLASH_OEn

2.5-V CMOS output

1

Flash Read Strobe

FLASH_WEn

2.5-V CMOS output

1

Flash Write Strobe

FLASH_BSYn

2.5-V CMOS input

1

Flash Busy

FLASH_CLK

2.5-V CMOS output

1

Flash Clock

FLASH_RSTn

2.5-V CMOS output

1

Flash Reset

FLASH_ADVn

2.5-V CMOS output

1

Flash Address Valid

FLASH_WPn

2.5-V CMOS output

1

Flash Write Protect

Resets

CPU_RESETn

2.5-V CMOS input

1

Nios

®

II CPU Reset

S4GT_RESETn

2.5-V CMOS input

1

S4GT General FPGA Reset

Switches, Buttons, LEDS

User Push Buttons

2.5-V CMOS input

6

6 User Push buttons

User DIP Switches

2.5-V CMOS input

8

8 User DIP Switches

User LEDS

2.5-V CMOS output

8

8 User LEDs (Green)

HEX Rotary Switch

2.5-V CMOS input

4

16 Position Rotary Switch

User I/Os

2.5-V CMOS inout

4

4 User I/O pins to header field

LCD

16 Character × 2 Line LCD

2.5-V CMOS

11

LCD

Ethernet

TXD[3:0]

2.5-V CMOS output

4

Ethernet Transmit RGMII Data Bus

TXEN

2.5-V CMOS output

1

Ethernet Transmit Enable

GTXCLK

2.5-V CMOS output

1

Ethernet Transmit Clock

RXD[3:0]

2.5-V CMOS input

4

Ethernet Receive RGMII Data Bus

RXDV

2.5-V CMOS input

1

Receive Data Valid

RXCLK

2.5-V CMOS input

1

Receive Clock

MDC

2.5-V CMOS input

1

Ethernet MII Clock

MDIO

2.5-V CMOS inout

1

Ethernet MII Data

ENET_SGMII_TXP/N

LVDS output

2

Ethernet SGMII Transmit Data Positive/Negative

ENET_SGMII_RXP/N

LVDS input

2

Ethernet SGMII Receive Data Positive/Negative

Transceivers

GXB0 Transmit Channel

Transceiver channel

12

Six matched length GXB0 transmit channels

routed to a backplane connector J70.

GXB0 Receive Channel

Transceiver channel

12

Six matched length GXB0 receive channels routed

to a backplane connector J71.

Table 2–4. Stratix IV GT I/O Usage Summary (Part 2 of 3)

Function

I/O Type

I/O Count

Description