Altera Active Serial Memory Interface User Manual

Page 7

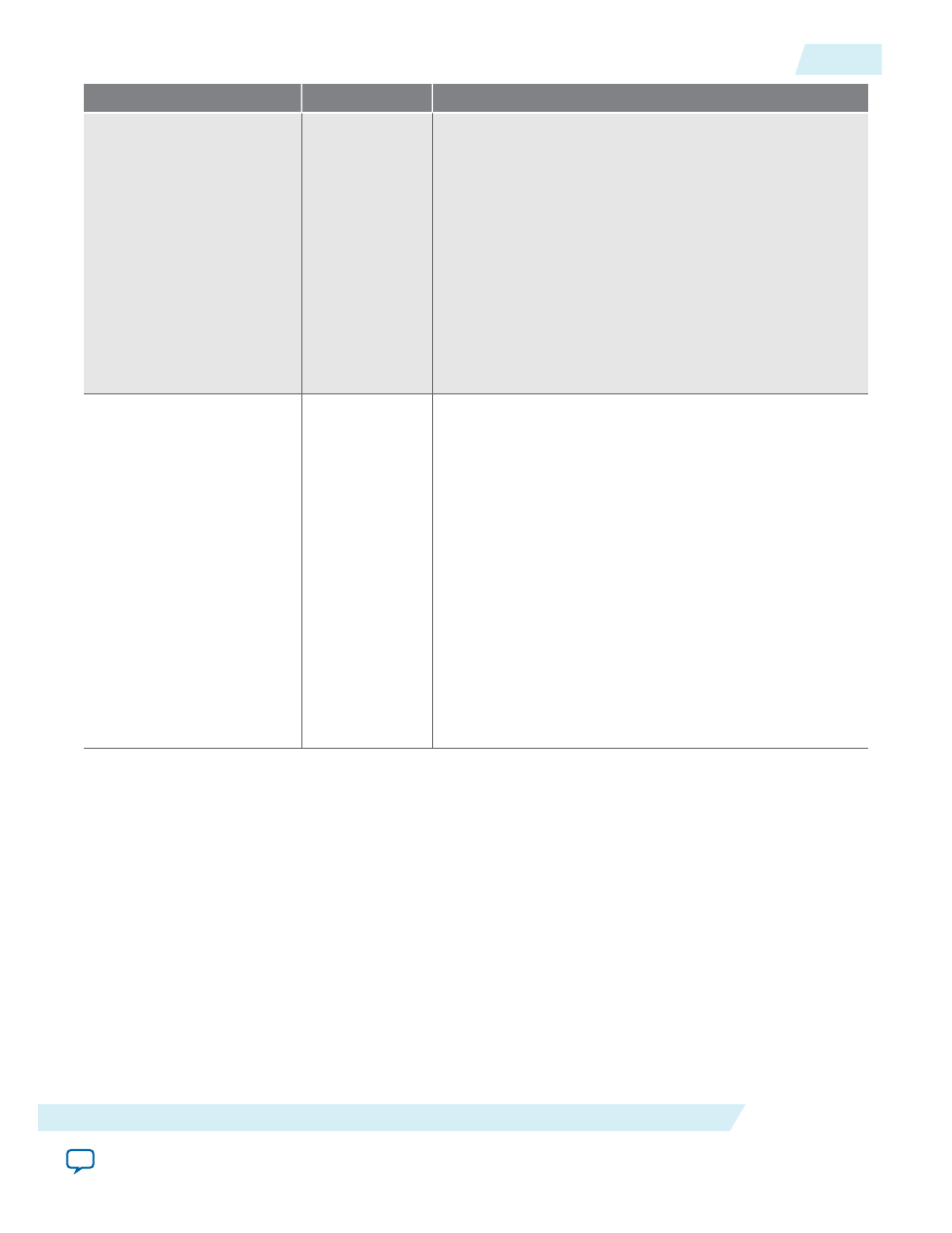

Parameter

Legal Values

Descriptions

Write mode

—

• This option is only available when you turn on the

Enable ‘write’ operation option.

• When you select this option, the Altera ASMI Parallel

IP core defines two parameters, which are PAGE_SIZE

and PORT_SHIFT_BYTES for the following writing

mode to the EPCS/EPCQ/EPCQ-L device:

Single byte write: PAGE_SIZE = 1, PORT_SHIFT_

BYTES = PORT_UNUSED

Page write: PAGE_SIZE = 1 to 256, if 1 then PORT_

SHIFT_BYTES = PORT_UNUSED, else PORT_USED

Store ‘page write’ data in logic elements.

Use ‘fast_read’ port

—

• Enables the ability to perform a fast read operation

with an active-high input signal named

fast_read

.

When this signal is asserted, the IP core performs a fast

read from the memory address that appears on the

addr[23..0]

signal. Each data byte appears on the

dataout[7..0]

signal as it is read. For EPCQ256/

EPCQ-L256 or larger devices, the width of the

addr

and

read_address

signals is 32 bit.

• The

fast_read

signal supports single-byte fast read

and sequential fast read. If a write or erase operation is

in progress (the busy signal is asserted), the fast read

command is ignored. The fast read operation occurs

only when allowed by the

rden

signal.

• This option is available for all EPCS/EPCQ/EPCQ-L

devices, except for EPCS1 and EPCS4 devices.The fast

read operation replaces the normal settings.

UG-ALT1005

2014.12.15

Parameters

7

Altera ASMI Parallel IP Core User Guide

Altera Corporation