Altera Active Serial Memory Interface User Manual

Page 13

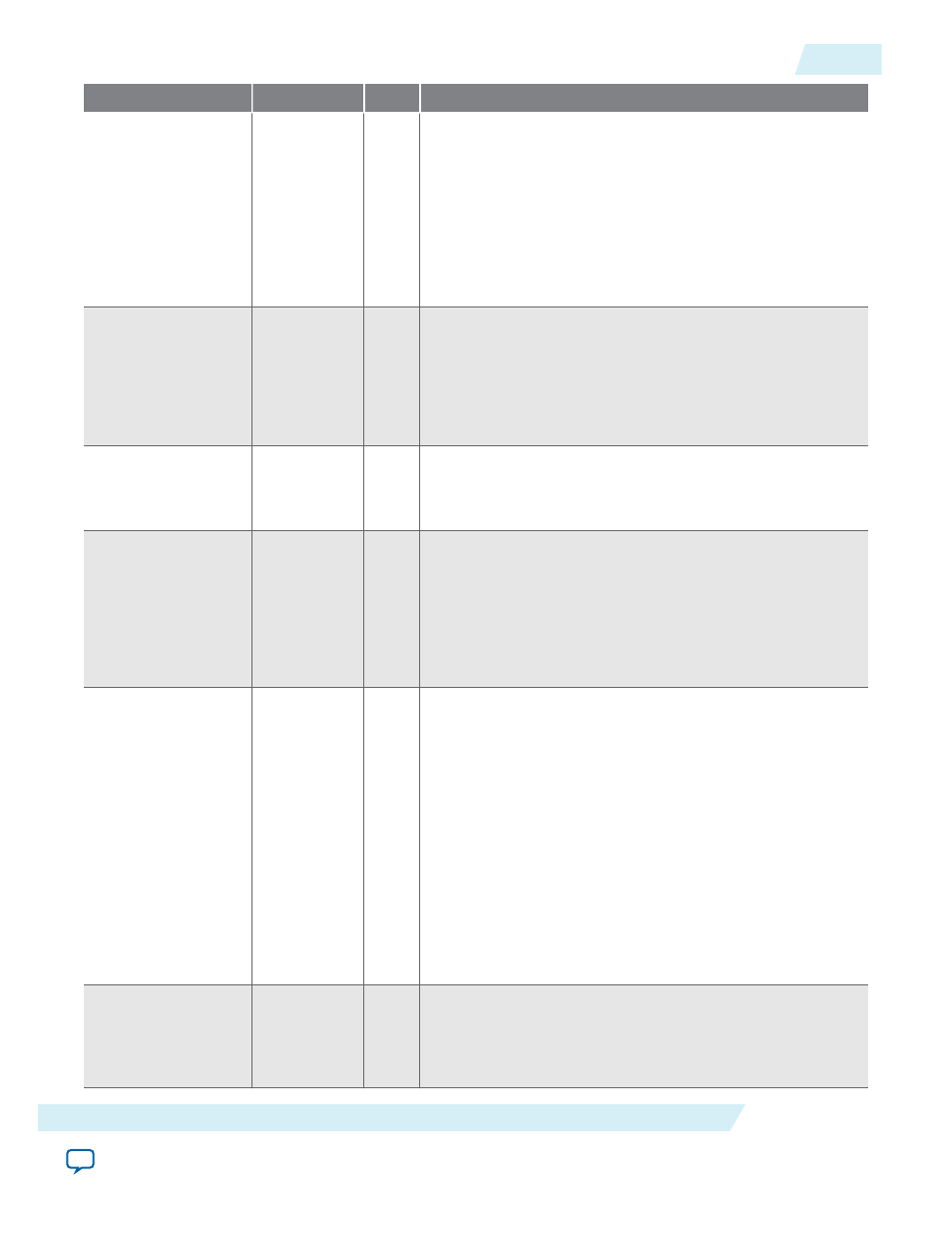

Port

Condition

Size

Descriptions

ex4b_addr

Optional

1 bit To exit the 4-byte addressing mode when you use an

EPCQ256/EPCQ-L256 or larger devices, pull the WREN

signal high, followed by at least one clock cycle. If WREN

signal is zero, the 4-byte addressing mode exit operation will

not be carried out even though the ex4b_addr is high. After

the IP core receives the command, the IP core asserts the

busy signal to indicate that the exit operation is in progress.

If you select EPCQ256/EPCQ-L256 or larger devices as your

configuration device, this port is required.

fast_read

Optional

1 bit Active-high port that executes the fast read operation. If

asserted, the IP core performs a fast read operation from a

memory address value that appears on the

addr[23..0]

port. For EPCQ256/EPCQ-L256 or larger devices, the width

of the

addr

and

read_address

signals is 32 bit.

Use the

fast_read

port together with the

rden

port.

rden

Required

1 bit Active-high port that allows read and fast read operations to

be performed as long as it stays asserted. This port is only

for Altera ASMI Parallel IP core and not the configuration

device.

read

Required

1 bit Active-high port that executes the read operation. If

asserted, the IP core performs a read operation from a

memory address value that appears on the

addr[23..0]

port. For EPCQ256/EPCQ-L256 or larger devices, the width

of the

addr

and

read_address

signals is 32 bit.

Use the

read

port together with the

rden

port. The

read

port is disabled if the

fast_read

port is used.

read_dummyclk

Optional

1 bit By pulling high the

read_dummyclk

signal for at least one

clock cycle, the Altera ASMI Parallel IP core reads the

device dummy cycles from a volatile register and stores the

value in a register. You can use the stored value for fast read

operation without changing the dummy cycles (if the

dummy cycles is different from designated value). The

stored value is hold until the next high

read_dummyclk

signal or power cycle of FPGA.

When you enable this option, the dummy clock value is read

from a non-volatile register of an EPCQ/EPCQ-L device, by

default. If asserted high, the dummy clock value changes to

the dummy clock value read from a volatile register.

When you disable this option, the dummy clock used in the

IP core is as per default in the EPCQ/EPCQ-L device.

read_rdid

Optional

1 bit Active-high port that executes the read memory capacity ID

operation. If asserted, the IP core proceeds to read the

memory capacity ID of the EPCS/EPCQ/EPCQ-L device,

and the value of the memory capacity ID appears at the

rdid_out[7..0]

port.

UG-ALT1005

2014.12.15

Input Ports

13

Altera ASMI Parallel IP Core User Guide

Altera Corporation