Altera Active Serial Memory Interface User Manual

Page 30

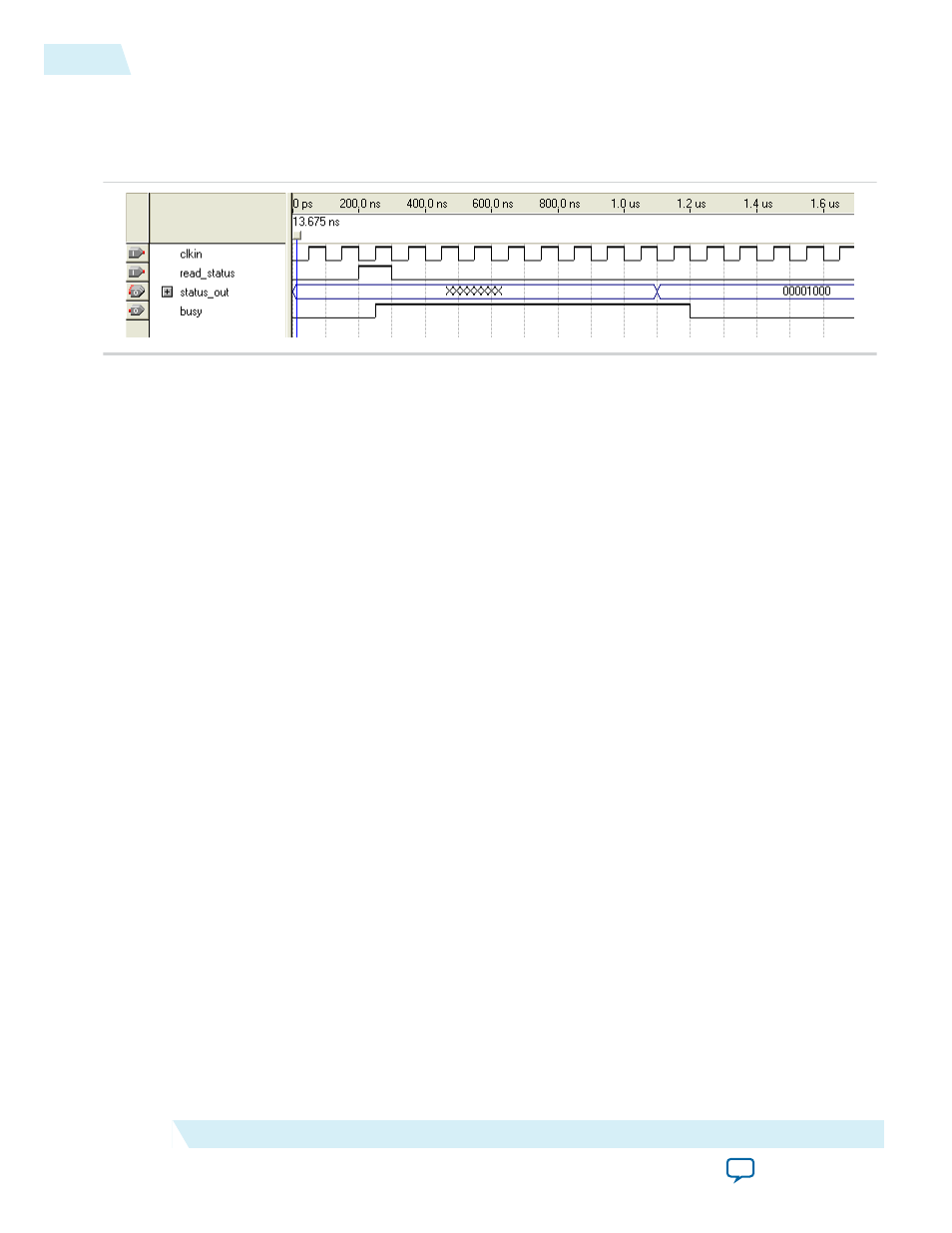

Figure 14: Reading a Status Register

This figure shows an example of the latency when the Altera ASMI Parallel IP core is executing the read

status register command. The latency shown does not correctly reflect the true processing time. It shows

the command only.

The IP core registers the

read_status

signal on the rising edge of the

clkin

signal. After the IP

core receives the

read_status

signal, it asserts the

busy

signal to indicate that the read command

is in progress. To prevent the IP core from re-registering the command and executing it again,

deassert the

read_status

signal before the

busy

signal is deasserted.

The IP core ensures that the 8-bit status register value is available on the

status_out[7..0]

signal before deasserting the

busy

signal. You can sample the

status_out[7..0]

signal as soon

as the

busy

signal is deasserted.

You must decode the 8-bit status register value to find out which sectors are protected.

The

status_out[7..0]

signal holds the value of the status register from the last read status

command. The contents of the status register may have changed (via a sector protect command,

for example). Therefore, before sampling the

status_out[7..0]

signal, you must issue a new

read status command.

Erase Memory in a Specified Sector on the EPCS/EPCQ/EPCQ-L Device

Use the

sector_erase

signal to instruct the IP core to erase memory in a specified sector on the EPCS/

EPCQ/EPCQ-L device.

30

Erase Memory in a Specified Sector on the EPCS/EPCQ/EPCQ-L Device

UG-ALT1005

2014.12.15

Altera Corporation

Altera ASMI Parallel IP Core User Guide