Epcq/epcq-l devices read dummy clock instruction, Write data to the epcs/epcq/epcq-l device – Altera Active Serial Memory Interface User Manual

Page 26

when selecting EPCQ/EPCQ-L quad I/O fast read operation, the IP core generates the first byte of data on

the

dataout[7..0]

port after ten cycles, and then it appears for the read command.

If the

rden

signal is asserted for the subsequence data, the data from the next address appears on the

dataout[7..0]

port at every eight clock cycles for standard I/O, every four clock cycles for dual I/O, and

every two clock cycles for quad I/O. Monitor the

data_valid

signal to ensure that you sample the

dataout[7..0]

signal only when the

data_valid

signal is asserted.

When you enable multiple I/O in fast read operation, the fast read and write operations have their

equivalents in multiple I/O. Instruction operation codes are sent in DQ0 and the rest of data will be

transferred in multiple data lines. Other instructions such as sector erase, read status, and others still

operates in standard I/O mode.

EPCQ/EPCQ-L Devices Read Dummy Clock Instruction

By default, the Altera ASMI Parallel IP core disables the Read device dummy clock option and uses the

Although you can configure the dummy clock value in the EPCQ device, the dummy clock value must be

in accordance to the value in the

If you

configure the dummy clock value in the EPCQ/EPCQ-L device other than default value, the fast read

operation fails.

To perform the fast read operation without changing the dummy clock value in the EPCQ/EPCQ-L

device, enable the Read device dummy clock option. The Altera ASMI Parallel IP core configures the

dummy clock value to match with the EPCQ/EPCQ-L device. When enabling the Read device dummy

clock option, the Altera ASMI Parallel IP core reads the nonvolatile configuration register of the EPCQ/

EPCQ-L device for the dummy clock value at the beginning of clock cycles. This dummy clock value is

held until the

read_dummyclk

signal is asserted or until the device resets.

To read the dummy clock value from the volatile configuration register of the EPCQ/EPCQ-L device,

assert at least one clock cycle of the

read_dummyclk

signal. The Altera ASMI Parallel IP core asserts the

busy

signal after receiving the

read_dummyclk

signal. The

busy

signal remains asserted to indicate

operation is in progress and deasserted whenever the operation is completed. If the

read_dummyclk

signal

remains asserted while the busy signal is deasserted after the IP core finishes the operation, the IP core re-

registers the operation and carries out the operation again. So, the

read_dummyclk

signal must be

deasserted before the

busy

signal is deasserted. The dummy clock value is held until the next

read_dummyclk

signal is asserted or until the device resets.

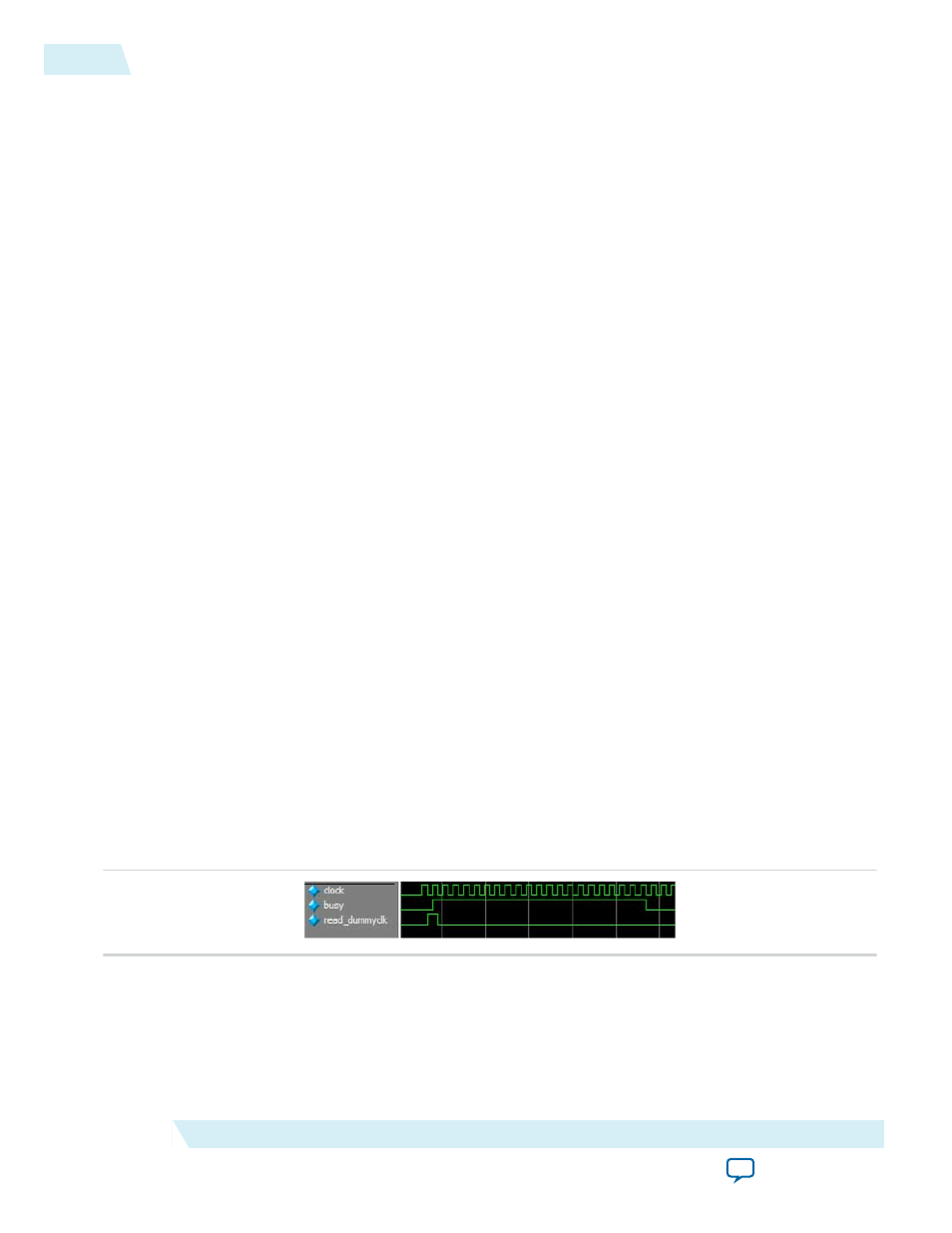

Figure 10: Read Dummy Clock Instruction

This figure does not reflect the true processing time.

Write Data to the EPCS/EPCQ/EPCQ-L Device

The Altera ASMI Parallel IP core supports two types of write operation: single-byte write and page-write.

26

EPCQ/EPCQ-L Devices Read Dummy Clock Instruction

UG-ALT1005

2014.12.15

Altera Corporation

Altera ASMI Parallel IP Core User Guide