Altera Active Serial Memory Interface User Manual

Page 15

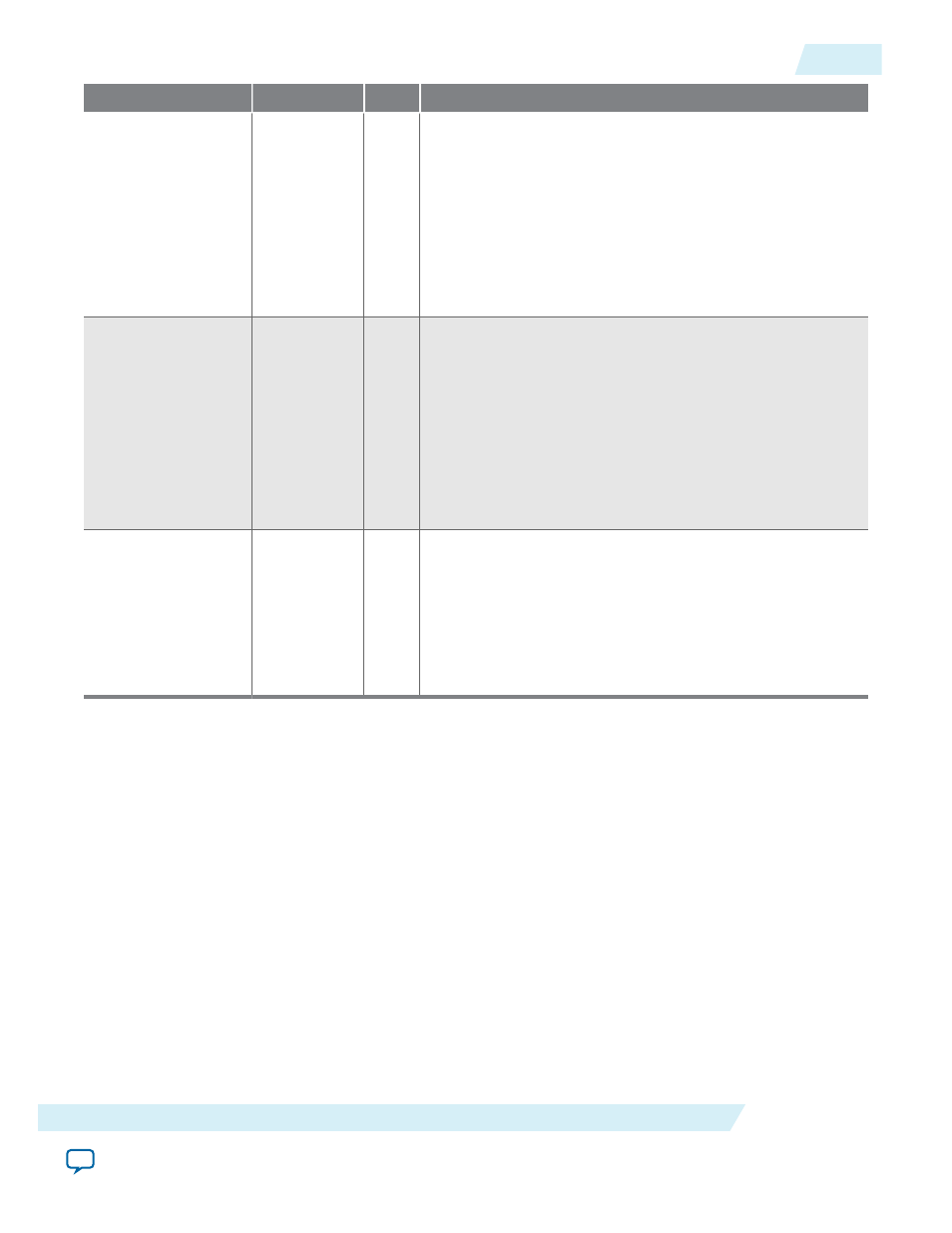

Port

Condition

Size

Descriptions

wren

Optional

1 bit Active-high port that allows write and erase operations to be

performed as long as it stays asserted. If the IP core does not

generate this port, the IP core automatically allows all write

and erase operations. Use this port with the following ports:

•

write

•

sector_protect

•

bulk_erase

•

sector_erase

•

die_erase

write

Optional

1 bit Active-high port that executes the write operation. If

asserted, the IP core writes the data from the

datain[7..0]

port (for single-byte write), or from the page-write buffer

(for page-write), to the memory address specified in the

addr[23..0]

port (and to the subsequent addresses for page

write operation). For EPCQ256/EPCQ-L256 or larger

devices, the width of the

addr

and

read_address

signals is

32 bit.

In page-write operation, you must use the

shift_bytes

port to shift in data bytes before asserting the write port.

sce[]

Optional

3 bit Select targeted flash for desired operation by controlling

FPGA

nCSO[2..0]

pin

• 3'b000 (default value)/ 3'b001: select flash connected to

nCSO[0]

• 3'b010: select flash connected to

nCSO [1]

• 3'b100: select flash connected to

nCSO [2]

sce[]

is only available for Arria 10 devices

Related Information

• on page 33

For more information about

en4b_addr

signal

• on page 23

For more information about the fast read operation

• on page 18

For more information about read, fast read, write and erase operations

• on page 22

For more information about the read operation

• on page 19

For more information about the read memory capacity ID operation

• on page 20

For more information about the read silicon ID operation

• on page 29

For more information about the read EPCS/EPCQ status register operation

• on page 30

For more information about the sector erase operation

UG-ALT1005

2014.12.15

Input Ports

15

Altera ASMI Parallel IP Core User Guide

Altera Corporation