Altera Active Serial Memory Interface User Manual

Page 33

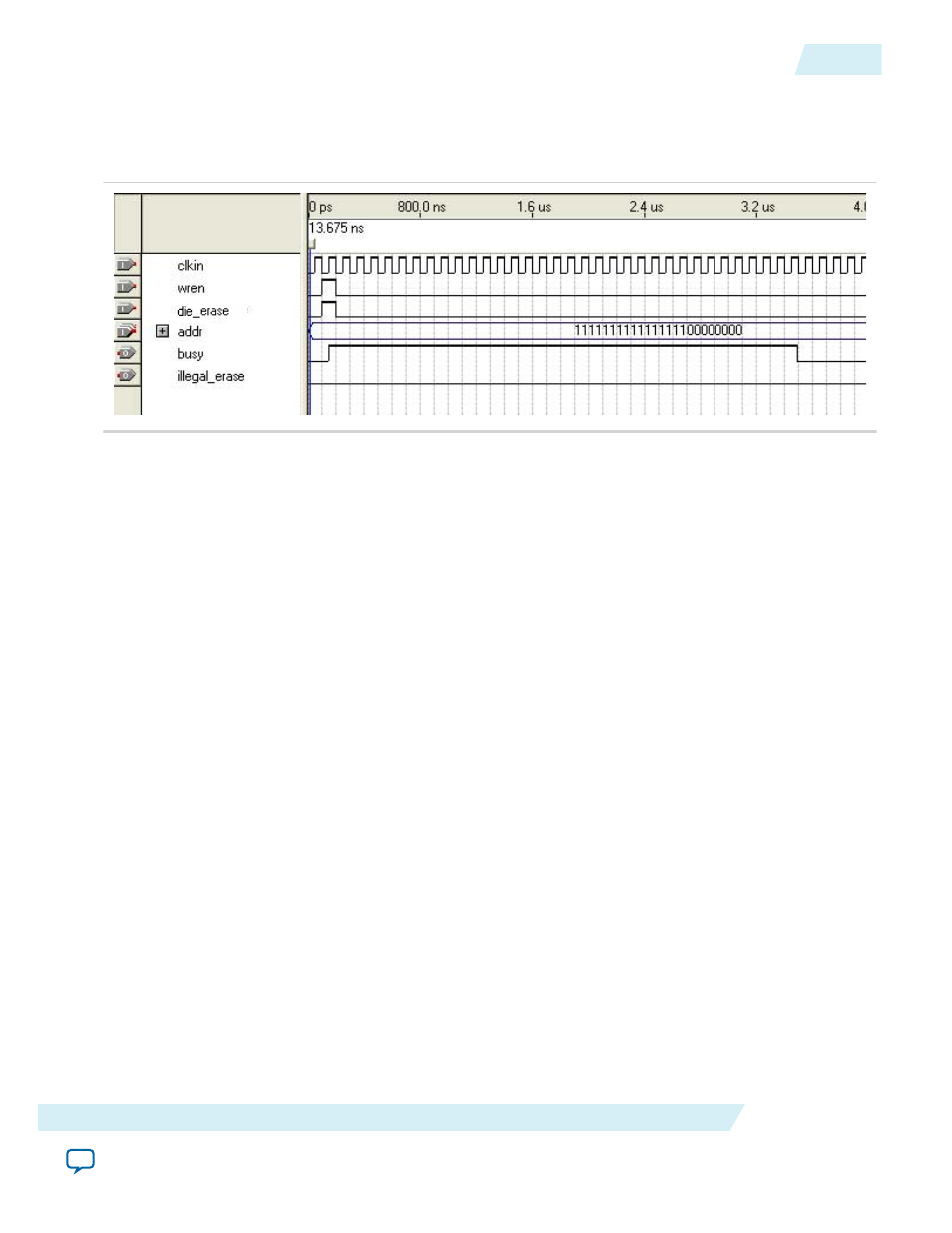

Figure 17: Erasing Memory in a Specified Die

This figure shows an example of the latency when the Altera ASMI Parallel IP core is executing the erase

memory command. The latency shown does not correctly reflect the true processing time. It shows the

command only.

The IP core registers the

die_erase

signal on the rising edge of the

clkin

signal. The address placed on

the

addr[31..0]

signal is a valid address in the die that you can erase.

Ensure that the memory address to be erased appears on the

addr[31..0]

signal before setting the

wren

and

die_erase

signals to a value of one. After the IP core receives the die erase command, the IP core

asserts the busy signal when erasing the die.

If

wren

signal has a value of zero, then the die erase operation is carried out, and the busy signal remains

deasserted.

If the memory region is protected (specified in the EPCQ-L status register), the erase operation cannot

proceed, and the busy signal is deasserted. The

illegal_erase

port is then asserted for two clock cycles

to indicate that the erase operation has been cancelled.

If you keep the

wren

and

die_erase

signals asserted while the busy signal is deasserted after the IP core

has finished erasing the memory, the IP core re-registers the

wren

and

die_erase

signals as a value of one

and carries out another die erase operation. Therefore, before the IP core deasserts the busy signal, you

must deassert the

wren

and

die_erase

signals.

Enable 4-byte Addressing Operation for an EPCQ256/EPCQ-L256 or Larger Devices

The

en4b_addr

input port allows you to access all memory address of an EPCQ256/EPCQ-L256 or larger

devices. These input ports are available when you use an EPCQ256/EPCQ-L256 or larger devices.

Note: The 4-byte addressing operation is supported for EPCQ256/EPCQ-L256 or larger devices only, so

you must enable 4-byte addressing when you use an EPCQ256/EPCQ-L256 or larger devices.

To enable 4-byte addressing mode, pull the write enable signal (

wren

) high, followed by the

en4b_addr

signal for at least one clock cycle. If the

wren

signal has a value of zero, the 4-byte addressing operation

will not be carried out even though the

en4b_addr

signal is being pulled to high. After the IP core receives

the 4-byte addressing command, the IP core asserts the busy signal to indicate the operation is in

progress.

UG-ALT1005

2014.12.15

Enable 4-byte Addressing Operation for an EPCQ256/EPCQ-L256 or Larger Devices

33

Altera ASMI Parallel IP Core User Guide

Altera Corporation