Input ports – Altera Active Serial Memory Interface User Manual

Page 12

• on page 31

For more information about the Use ‘bulk_erase’ port parameter

• on page 30

For more information the Use 'sector_erase' port parameter. The value of the signal for the Use

'sector_erase' port parameter is a valid address in the sector.

Input Ports

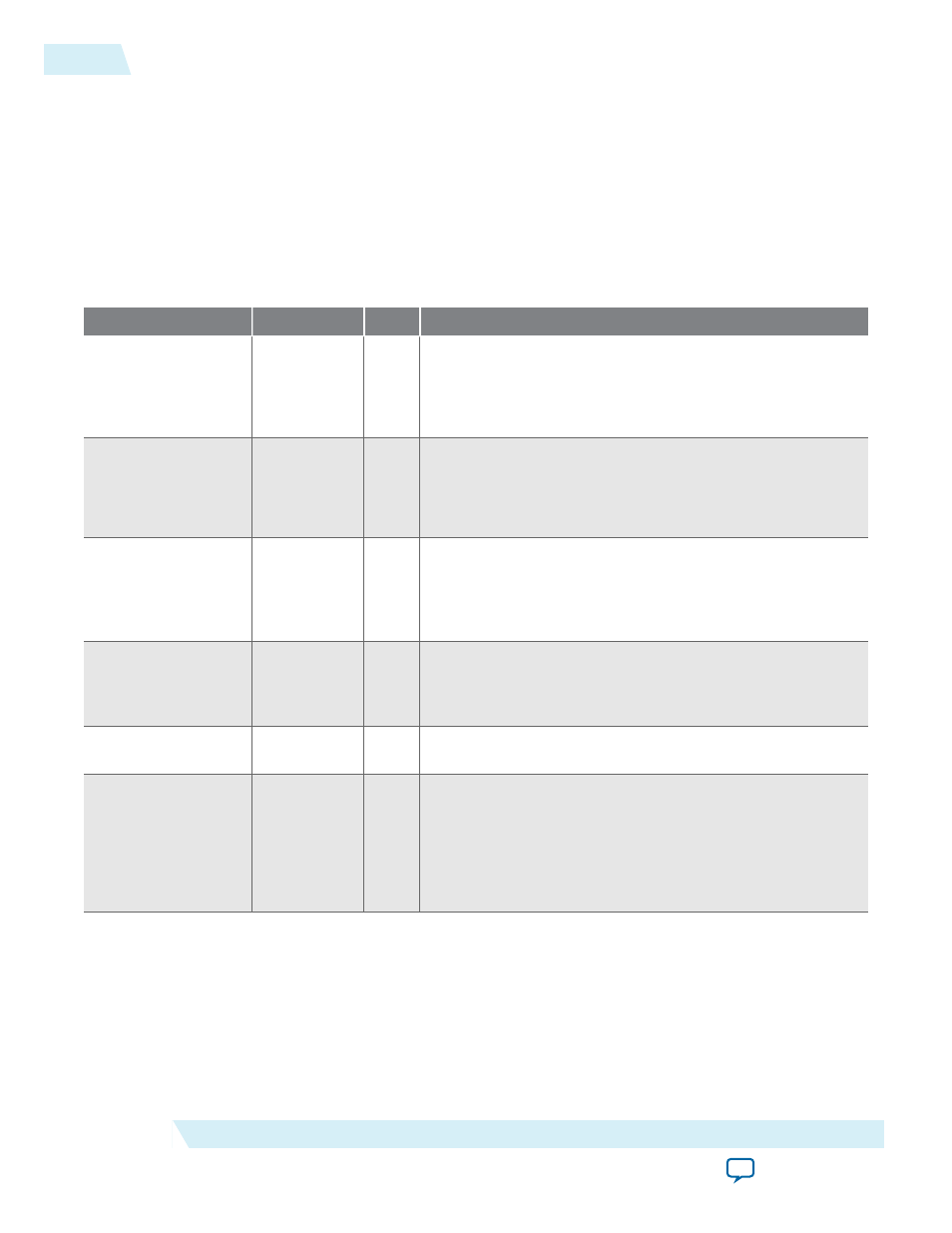

This table lists the input ports for the Altera ASMI Parallel IP core.

Table 2: Input Ports

Port

Condition

Size

Descriptions

addr[]

Required

24 or

32 bit

Contains the value of the EPCS/EPCQ/EPCQ-L memory

address to be read from, written to, and erased from.

For EPCQ256/EPCQ-L256 or larger devices, the width of

the

addr[]

is 32 bit.

asmi_dataout[]

Optional

1 bit Input port to feed data from EPCS/EPCQ/EPCQ-L device if

select the Disable dedicated Active Serial interface option.

If you are using Arria

®

V, Cyclone

®

V, Stratix

®

V, or Arria

10 devices, then the bit size is 4 bit.

bulk_erase

Optional

1 bit Active-high port that executes the bulk erase operation. If

asserted, the IP core performs a full-erase operation that sets

all memory bits of the EPCS/EPCQ/EPCQ-L256 device to

‘1’, which includes the general purpose memory of the

EPCS/EPCQ/EPCQ-L device.

clkin

Required

1 bit Input clock port for the ASMI block. In general, the

clkin

signal must toggle at the appropriate frequency range at all

times. The IP core uses the signal to feed the EPCS/EPCQ/

EPCQ-L device and to perform internal processing.

datain[]

Optional

8 bit Parallel input data of 1-byte length for write and sector

protect operations.

en4b_addr

Required

1 bit When you select EPCQ256/EPCQ-L256 or larger devices as

your configuration device, address width will change from

0..23

to

0..31

. EPCQ256 supports Dual and Quad data

width.

If you select EPCQ256/EPCQ-L256 or larger devices as your

configuration device, this port is required.

12

Input Ports

UG-ALT1005

2014.12.15

Altera Corporation

Altera ASMI Parallel IP Core User Guide