6 addresses in the process image, Addresses in the process image – Pilz PSSu E S 2AI U User Manual

Page 21

Function description

Operating Manual PSSu E S 2AI U(T)

21405EN03

21

4.2.6

Addresses in the process image

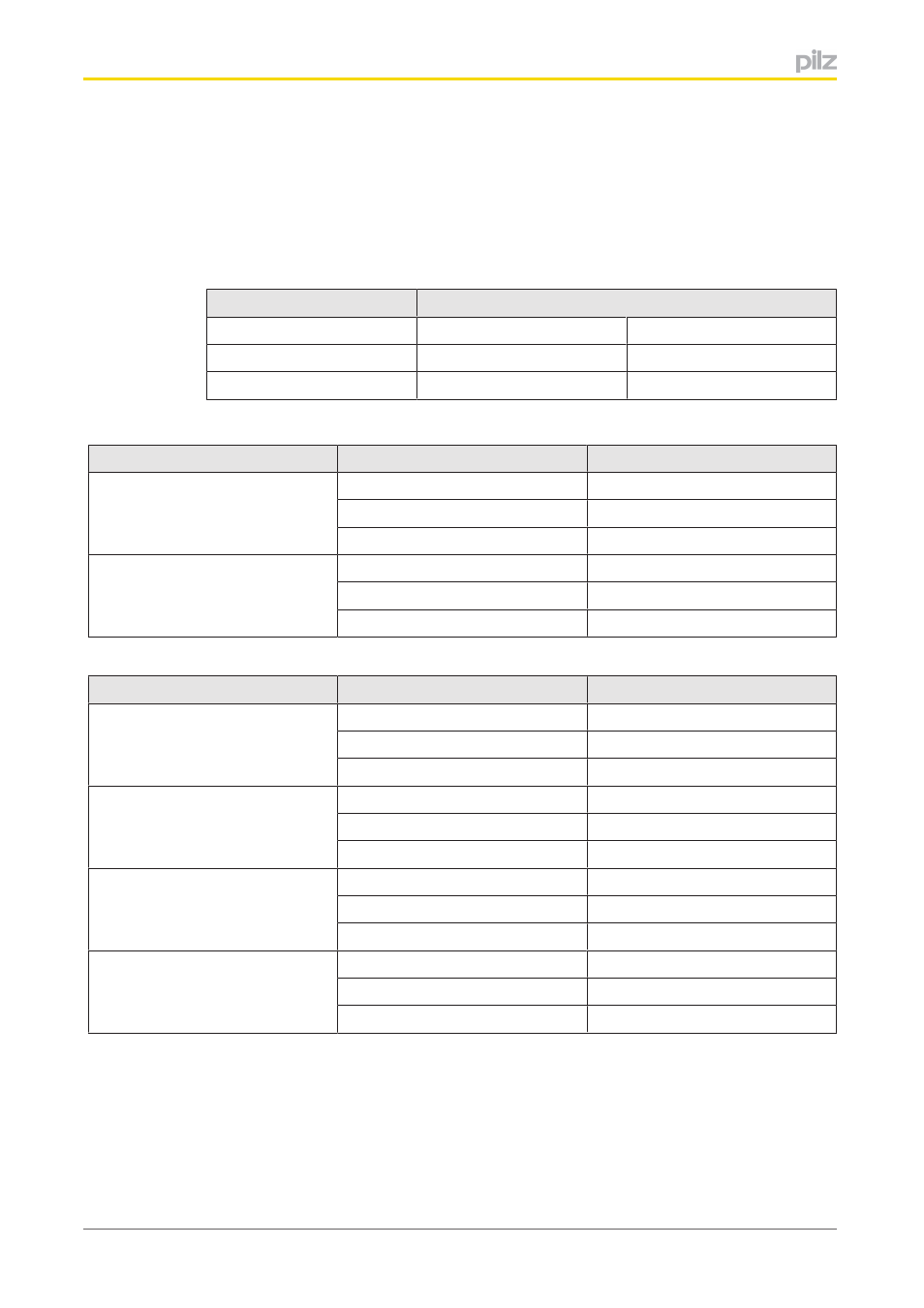

Each input occupies 16 consecutive bit addresses for the input data. Each input occupies

an additional 8 consecutive bit addresses for the status byte, where this has been con

figured for the input. If the status byte is configured to be transferred without input data,

each input occupies 8 consecutive bit addresses. All the status bytes are displayed first in

the PII, followed by the input data.

Configuration

Standard bus system

STPII

STPIO

Send input data

32 Bit

Send status byte ("R")

16 Bit

Bit sequence in the PII, input data only, no status byte:

Input

PII

Assignment

Input I0

1

LSB input data

...

...

16

MSB input data

Input I1

17

LSB input data

...

...

32

MSB input data

Bit sequence in the PII, input data and status byte:

Input

PII

Assignment

Input I0

1

LSB status byte

...

...

8

MSB status byte

Input I1

9

LSB status byte

...

...

16

MSB status byte

Input I0

17

LSB input data

...

...

32

MSB input data

Input I1

33

LSB input data

...

...

48

MSB input data

Bit sequence in the PII, status byte only, no input data: