Cypress enCoRe CY7C602xx User Manual

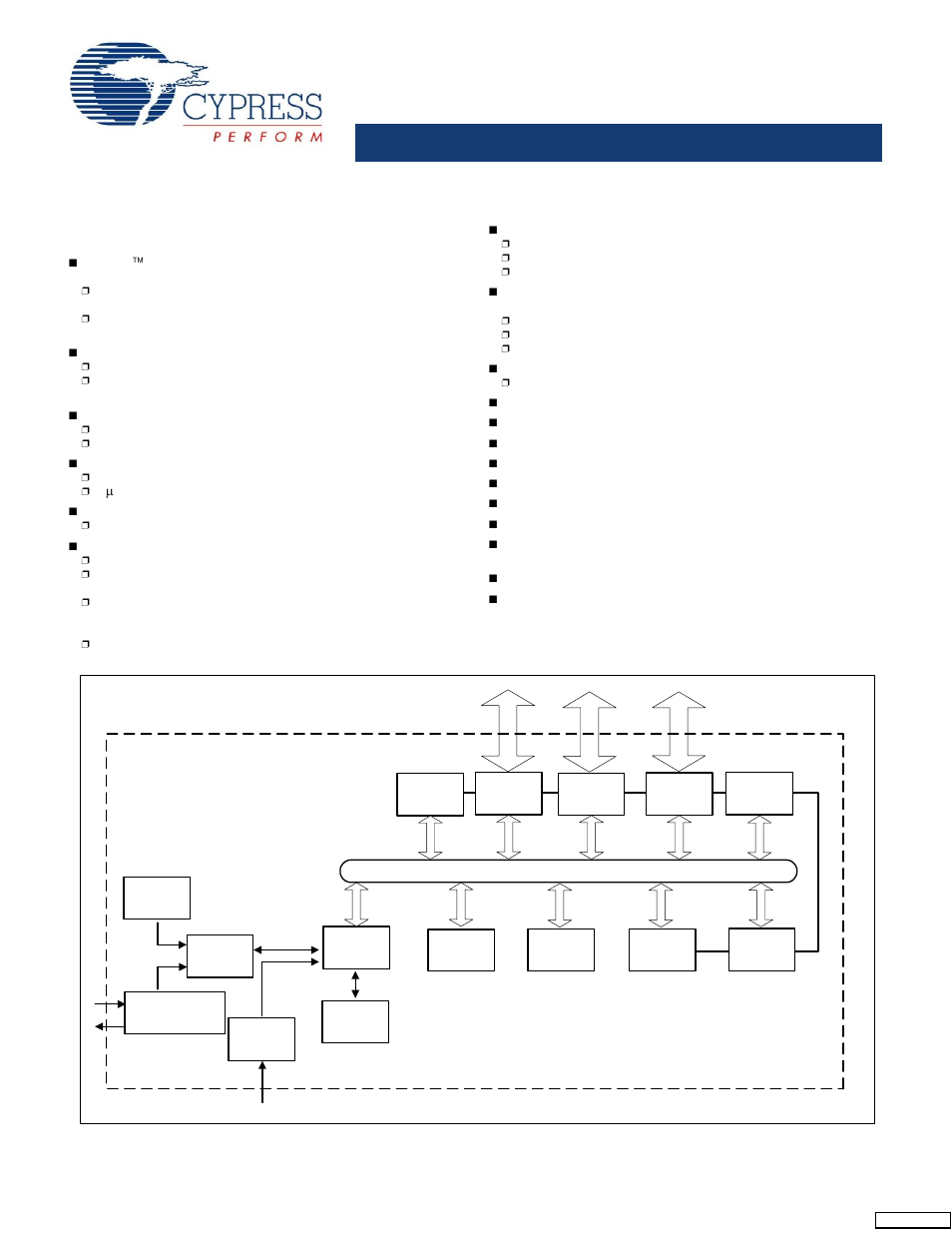

Encore™ ii low voltage microcontroller, Features, Logic block diagram

This manual is related to the following products:

Table of contents

Document Outline

- 1. Features

- 2. Logic Block Diagram

- 3. Applications

- 4. Introduction

- 5. Conventions

- 6. Pinouts

- 7. Register Summary

- 8. CPU Architecture

- 9. CPU Registers

- 9.1 Flags Register

- 9.2 Addressing Modes

- 9.2.1 Source Immediate

- 9.2.2 Source Direct

- 9.2.3 Source Indexed

- 9.2.4 Destination Direct

- 9.2.5 Destination Indexed

- 9.2.6 Destination Direct Source Immediate

- 9.2.7 Destination Indexed Source Immediate

- 9.2.8 Destination Direct Source Direct

- 9.2.9 Source Indirect Post Increment

- 9.2.10 Destination Indirect Post Increment

- 10. Instruction Set Summary

- 11. Memory Organization

- 12. Clocking

- 13. Reset

- 14. Sleep Mode

- 15. Low Voltage Detect Control

- 16. General Purpose IO Ports

- 16.1 Port Data Registers

- 16.2 GPIO Port Configuration

- 16.2.1 Int Enable

- 16.2.2 Int Act Low

- 16.2.3 TTL Thresh

- 16.2.4 High Sink

- 16.2.5 Open Drain

- 16.2.6 Pull Up Enable

- 16.2.7 Output Enable

- 16.2.8 SPI Use

- 16.2.9 P0.0/CLKIN Configuration

- 16.2.10 P0.1/CLKOUT Configuration

- 16.2.11 P0.2/INT0-P0.4/INT2 Configuration

- 16.2.12 P0.5/TIO0-P0.6/TIO1 Configuration

- 16.2.13 P0.7 Configuration

- 16.2.14 P1.0 Configuration

- 16.2.15 P1.1 Configuration

- 16.2.16 P1.2 Configuration

- 16.2.17 P1.3 Configuration (SSEL)

- 16.2.18 P1.4-P1.6 Configuration (SCLK, SMOSI, SMISO)

- 16.2.19 P1.7 Configuration

- 16.2.20 P2 Configuration

- 16.2.21 P3 Configuration

- 16.2.22 P4 Configuration

- 17. Serial Peripheral Interface (SPI)

- 18. Timer Registers

- 19. Interrupt Controller

- 20. Absolute Maximum Ratings

- 21. Ordering Information

- 22. Package Handling

- 23. Package Diagrams

- 24. Document History Page

- Sales, Solutions, and Legal Information