Cpu architecture, Cpu registers, 1 flags register – Cypress enCoRe CY7C602xx User Manual

Page 8

CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E

Page 8 of 68

8. CPU Architecture

This family of microcontrollers is based on a high performance,

8-bit, Harvard architecture microprocessor. Five registers control

the primary operation of the CPU core. These registers are

affected by various instructions, but are not directly accessible

through the register space by the user.

The 16-bit Program Counter Register (CPU_PC) directly

addresses the full 8 Kbytes of program memory space.

The Accumulator Register (CPU_A) is the general purpose

register that holds results of instructions that specify any of the

source addressing modes.

The Index Register (CPU_X) holds an offset value used in the

indexed addressing modes. Typically, this is used to address a

block of data within the data memory space.

The Stack Pointer Register (CPU_SP) holds the address of the

current top-of-stack in the data memory space. It is affected by

the PUSH, POP, LCALL, CALL, RETI, and RET instructions,

which manage the software stack. It is also affected by the SWAP

and ADD instructions.

The Flag Register (CPU_F) has three status bits: Zero Flag bit

[1]; Carry Flag bit [2]; Supervisory State bit [3]. The Global

Interrupt Enable bit [0] is used to globally enable or disable inter-

rupts. The user cannot manipulate the Supervisory State status

bit [3]. The flags are affected by arithmetic, logic, and shift opera-

tions. The manner in which each flag is changed is dependent

upon the instruction being executed (AND, OR, XOR). See

.

9. CPU Registers

9.1 Flags Register

The Flags Register is only set or reset with logical instruction.

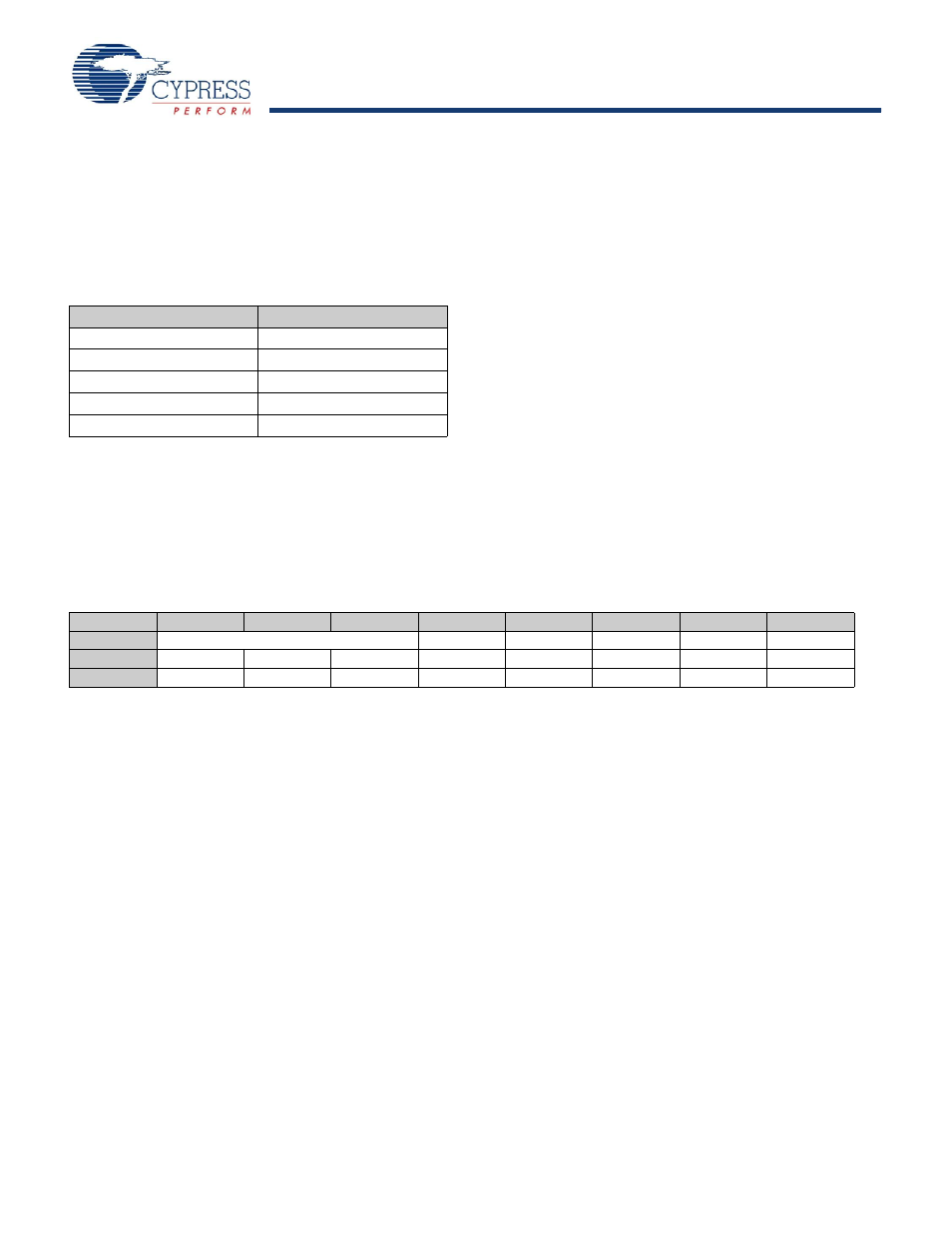

Table 8-1. CPU Registers and Register Name

Register

Register Name

Flags

CPU_F

Program Counter

CPU_PC

Accumulator

CPU_A

Stack Pointer

CPU_SP

Index

CPU_X

Table 9-1. CPU Flags Register (CPU_F) [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Reserved

XIO

Super

Carry

Zero

Global IE

Read/Write

–

–

–

R/W

R

R/W

R/W

R/W

Default

0

0

0

0

0

0

1

0

Bit [7:5]: Reserved

Bit 4: XIO

Set by the user to select between the register banks.

0 = Bank 0

1 = Bank 1

Bit 3: Super

Indicates whether the CPU is executing user code or supervisor code. (This code cannot be accessed directly by the user.)

0 = User Code

1 = Supervisor Code

Bit 2: Carry

Set by CPU to indicate whether there is a carry in the previous logical or arithmetic operation.

0 = No Carry

1 = Carry

Bit 1: Zero

Set by CPU to indicate whether there is a zero result in the previous logical or arithmetic operation.

0 = Not Equal to Zero

1 = Equal to Zero

Bit 0: Global IE

Determines whether all interrupts are enabled or disabled.

0 = Disabled

1 = Enabled

Note This register is readable with explicit address 0xF7. The OR F, expr and AND F, expr are used to set and clear the CPU_F

bits.