Reset – Cypress enCoRe CY7C602xx User Manual

Page 30

CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E

Page 30 of 68

13. Reset

The microcontroller supports two types of resets: Power on Reset (POR) and Watchdog Reset (WDR). When reset is initiated, all

registers are restored to their default states and all interrupts are disabled.

The occurrence of a reset is recorded in the System Status and Control Register (CPU_SCR). Bits within this register record the

occurrence of POR and WDR Reset respectively. The firmware interrogates these bits to determine the cause of a reset.

The microcontroller resumes execution from Flash address 0x0000 after a reset. The internal clocking mode is active after a reset,

until changed by user firmware.

Note The CPU clock defaults to 3 MHz (internal 24 MHz oscillator divide-by-8 mode) at POR to guarantee operation at the low V

CC

that might be present during the supply ramp.

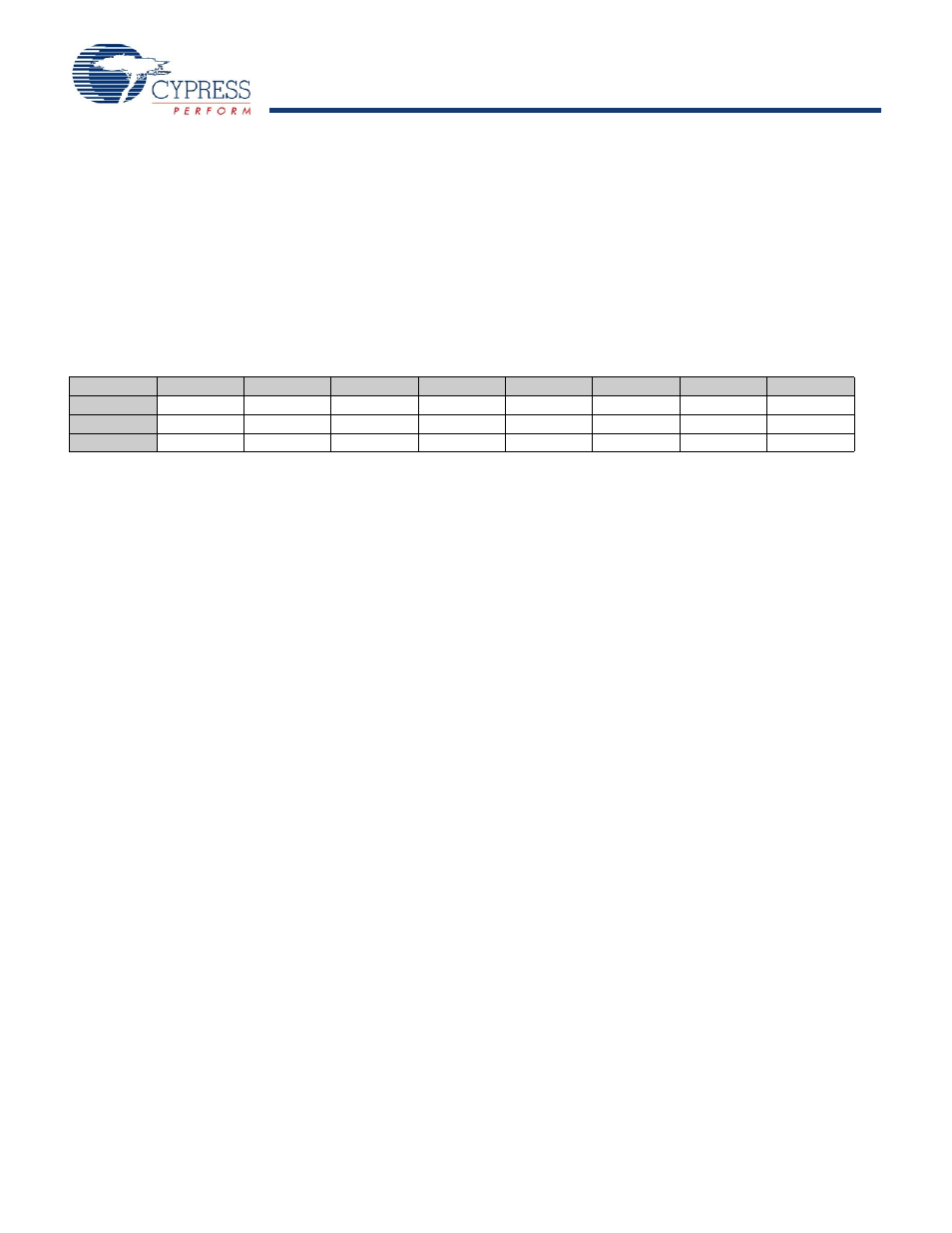

Table 13-1. System Status and Control Register (CPU_SCR) [0xFF] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

GIES

Reserved

WDRS

PORS

Sleep

Reserved

Reserved

Stop

Read/Write

R

–

R/C

[3]

R/C

R/W

–

–

R/W

Default

0

0

0

1

0

1

0

0

The bits of the CPU_SCR register are used to convey status and control of events for various functions of an enCoRe II LV device.

Bit 7: GIES

The Global Interrupt Enable Status bit is a read only status bit and its use is discouraged. The GIES bit is a legacy bit, which

was used to provide the ability to read the GIE bit of the CPU_F register. However, the CPU_F register is now readable. When

this bit is set, it indicates that the GIE bit in the CPU_F register is also set which, in turn, indicates that the microprocessor

services interrupts.

0 = Global interrupts disabled

1 = Global interrupt enabled

Bit 6: Reserved

Bit 5: WDRS

The WDRS bit is set by the CPU to indicate that a WDR event has occurred. The user can read this bit to determine the type of

reset that has occurred. The user can clear but not set this bit.

0 = No WDR

1 = A WDR event has occurred

Bit 4: PORS

The PORS bit is set by the CPU to indicate that a POR event has occurred. The user can read this bit to determine the type of

reset that has occurred. The user can clear but not set this bit.

0 = No POR

1 = A POR event has occurred. (Note that WDR events does not occur until this bit is cleared.)

Bit 3: SLEEP

Set by the user to enable CPU sleep state. CPU remains in sleep mode until any interrupt is pending. The Sleep bit is covered

in more detail in the

0 = Normal operation

1 = Sleep

Bit [2:1]: Reserved

Bit 0: STOP

This bit is set by the user to halt the CPU. The CPU remains halted until a reset (WDR, POR, or external reset) takes place. If

an application wants to stop code execution until a reset, the preferred method is to use the HALT instruction rather than writing

to this bit.

0 = Normal CPU operation

1 = CPU is halted (not recommended)