Cypress enCoRe CY7C602xx User Manual

Page 49

CY7C601xx, CY7C602xx

Document 38-16016 Rev. *E

Page 49 of 68

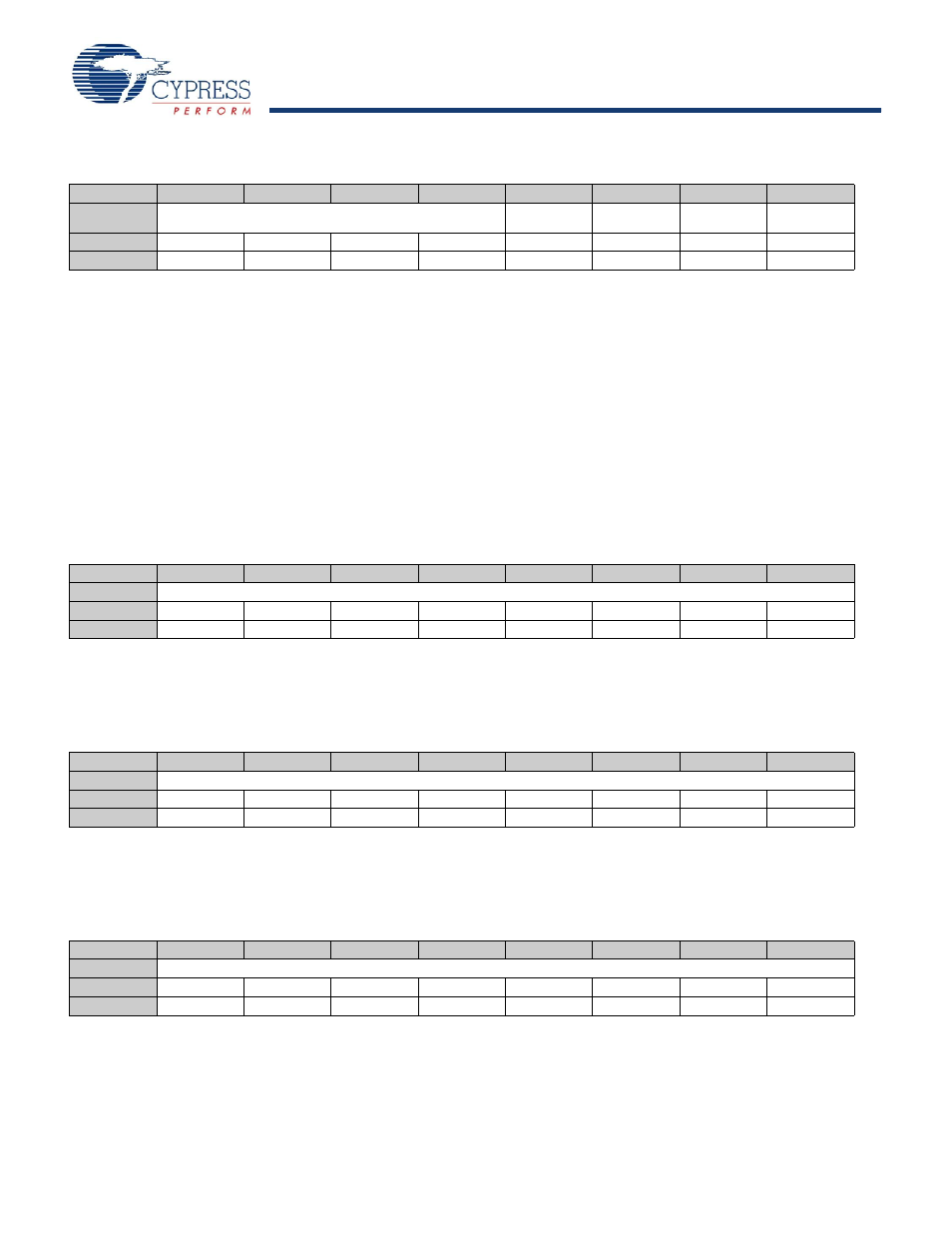

Table 18-4. Capture Interrupt Enable (TCAPINTE) [0x2B] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Reserved

Cap1 Fall

Enable

Cap1 Rise

Enable

Cap0 Fall

Enable

Cap0 Rise

Enable

Read/Write

–

–

–

–

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit [7:4]: Reserved

Bit 3: Cap1 Fall Enable

0 = Disable the capture 1 falling edge interrupt

1 = Enable the capture 1 falling edge interrupt

Bit 2: Cap1 Rise Enable

0 = Disable the capture 1 rising edge interrupt

1 = Enable the capture 1 rising edge interrupt

Bit 1: Cap0 Fall Enable

0 = Disable the capture 0 falling edge interrupt

1 = Enable the capture 0 falling edge interrupt

Bit 0: Cap0 Rise Enable

0 = Disable the capture 0 rising edge interrupt

1 = Enable the capture 0 rising edge interrupt

Table 18-5. Timer Capture 0 Rising (TCAP0R) [0x22] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Capture 0 Rising [7:0]

Read/Write

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

Bit [7:0]: Capture 0 Rising [7:0]

This register holds the value of the free running timer when the last rising edge occurred on the TIO0 input. When Capture 0 is

in 8-bit mode, the bits that are stored here are selected by the Prescale [2:0] bits in the Timer Configuration register. When

Capture 0 is in 16-bit mode this register holds the lower order eight bits of the 16-bit timer.

Table 18-6. Timer Capture 1 Rising (TCAP1R) [0x23] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Capture 1 Rising [7:0]

Read/Write

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

Bit [7:0]: Capture 1 Rising [7:0]

This register holds the value of the free running timer when the last rising edge occurred on the TIO1 input. The bits that are

stored here are selected by the Prescale [2:0] bits in the Timer Configuration register. When Capture 0 is in 16-bit mode this

register holds the high order eight bits of the 16-bit timer from the last TIO0 rising edge.

Table 18-7. Timer Capture 0 Falling (TCAP0F) [0x24] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Capture 0 Falling [7:0]

Read/Write

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

Bit [7:0]: Capture 0 Falling [7:0]

This register holds the value of the free running timer when the last falling edge occurred on the TIO0 input. When Capture 0 is

in 8-bit mode, the bits that are stored here are selected by the Prescale [2:0] bits in the Timer Configuration register. When

Capture 0 is in 16-bit mode this register holds the lower order eight bits of the 16-bit timer.